# UNIVERSIDADE TECNOLÓGICA FEDERAL DO PARANÁ CURSO DE ENGENHARIA DE COMPUTAÇÃO

EDUARDO FELIPE WEBER

# PROJETO E MODELO DE UM CONVERSOR BOOST INTERLEAVED

TRABALHO DE CONCLUSÃO DE CURSO

TOLEDO 2019

# EDUARDO FELIPE WEBER

# PROJETO E MODELO DE UM CONVERSOR BOOST INTERLEAVED

Trabalho de Conclusão de Curso apresentado ao Curso de Engenharia de Computação da Universidade Tecnológica Federal do Paraná - UTFPR Campus Toledo, como requisito parcial para a obtenção do título de Bacharel em Engenharia de Computação.

Orientador: Prof. Dr. Cassius Rossi de Aguiar Universidade Tecnológica Federal do Paraná

Ministério da Educação Universidade Tecnológica Federal do Paraná Campus Toledo Coordenação do Curso de Engenharia de Computação

## TERMO DE APROVAÇÃO

Título do Trabalho de Conclusão de Curso Nº 02

# Projeto e modelo de um conversor boost interleaved

por

Eduardo Felipe Weber

Esse Trabalho de Conclusão de Curso foi apresentado às **14h00 do dia 27 de novembro de 2019** como **requisito parcial** para a obtenção do título de **Bacharel em Engenharia de Computação**. Após deliberação da Banca Examinadora, composta pelos professores abaixo assinados, o trabalho foi considerado **APROVADO**.

Marcelo Oliveira Godinho USP São Carlos

Prof. Dr. Cassius Rossi de Aguiar Orientador - UTFPR Toledo

> Wagner Coelho Leal USP São Carlos

O termo de aprovação assinado encontra-se na coordenação do curso

### RESUMO

WEBER, Eduardo F. Projeto e modelo de um conversor *boost interleaved*. 2019. 0 f. Trabalho de Conclusão de Curso – Curso de Engenharia de Computação, Universidade Tecnológica Federal do Paraná. Toledo, 2019.

O objetivo deste trabalho é analisar e projetar um um conversor elevador de tensão utilizando a técnica *interleaved*, que melhora a resposta transitória da carga, tem melhor dissipação de calor e menos estresse nos semicondutores. Para representar o conversor *boost interleaved* em um modelo matemático, é utilizada a representação em espaço de estados, no qual é considerada a resistência parasita dos indutores e semicondutores. Nesse contexto, o conversor *boost interleaved* é controlado usando uma estrutura em cascata com o controle de corrente nos indutores no circuito interno e o controle de tensão do link CC no circuito externo. Após investigar a resposta dos controladores no domínio da frequência, indicando a estabilidade do sistema, o conversor é validado por simulações e medições experimentais destacando o correto funcionamento do sistema, atingindo a tensão desejada com pequena amplitude de ondulação residual. **Palavras-chave**: Coversor CC-CC. Eletrônica de Potência. Fotovoltaico.

## ABSTRACT

WEBER, Eduardo F. Model and Design of an Interleaved Boost Converter. 2019. 0 f. Trabalho de Conclusão de Curso – Curso de Engenharia de Computação, Universidade Tecnológica Federal do Paraná. Toledo, 2019.

The aim of this paper is to analyze and design a boost power converter utilizing the interleaved technique, which improves the load transient response, provides better heat dissipation and less stress on the semiconductors. To represent the interleaved boost converter in a mathematical model, its state space representation is used, where the parasitic resistance of the inductors and semiconductors is considered. In this context, the interleaved boost converter is controlled using a cascade structure with the input current on the inductors in the inner loop and the dc-link voltage in the outer loop. After investigating the response of the controllers in the frequency domain, indicating the stability of the system, the converter is validated by simulations and by experimental measurements highlighting the correct operation of the system, reaching the desired voltage with small residual ripple amplitude.

Keywords: DC-DC Converter. Power Electronics. Photovoltaic.

# LISTA DE FIGURAS

| Figura 1       –       Representação da técnica interleaved de N fases.       N         | 2  |

|-----------------------------------------------------------------------------------------|----|

| Figura 2 – Conversor <i>boost interleaved</i> proposto                                  | 2  |

| Figura 3 – Arranjo de painéis solares                                                   | 3  |

| Figura 4 – Exemplo da curva da corrente em função da tensão de um painel solar          | 3  |

| Figura 5 – Circuito equivalente para representar um painel solar                        | 3  |

| Figura 6 – Correlação entre a corrente dos indutores e o estado das chaves, adaptado de |    |

| Fuzato (2015)                                                                           | 4  |

| Figura 7 – Circuito equivalente do primeiro subintervalo                                | 4  |

| Figura 8 – Circuito equivalente do segundo subintervalo                                 | 5  |

| Figura 9 – Circuito equivalente do quarto subintervalo                                  | 6  |

| Figura 10 – Diagrama do controle proposto para o conversor                              | 8  |

| Figura 11 – Diagrama de Bode da corrente em malha aberta                                | 9  |

| Figura 12 – Diagrama de Bode da corrente em malha fechada                               | 9  |

| Figura 13 – Diagrama de Bode da tensão em malha aberta                                  | 9  |

| Figura 14 – Diagrama de Bode da tensão em malha fechada                                 | 9  |

| Figura 15 – Tensão de saída do conversor simulado                                       | 10 |

| Figura 16 – Entrada de corrente do conversor simulado                                   | 10 |

| Figura 17 – <i>Ripple</i> da corrente de entrada do conversor simulado                  | 10 |

| Figura 18 – Pico de tensão de saída em uma queda de potência de 1 kW para 333 W         | 10 |

| Figura 19 – Pico de corrende de entrada em uma queda de potência de 1 kW para 333 W     | 11 |

| Figura 20 – Pico de tensão de saída em um degrau de potência de 1 kW para 333 W         | 11 |

| Figura 21 – Pico de corrente de entrada em um degrau de potência de 1 kW para 333 W     | 11 |

| Figura 22 – Protótipo em uma placa de circuito impresso                                 | 10 |

| Figura 23 – Forma de onda dos acionadores das chaves                                    | 12 |

| Figura 24 – Inicialização do protótipo                                                  | 12 |

| Figura 25 – Protótipo em estado estacionário                                            | 12 |

| Figura 26 – Resposta pra uma mudança instantanêa de potência                            | 12 |

| Figura 27 – Resposta pra uma mudança instantanêa de potência em detalhes                | 13 |

|                                                                                         |    |

## LISTA DE TABELAS

| Tabela 1 | — | Especificação dos parâmetros de controle. | 10 |

|----------|---|-------------------------------------------|----|

| Tabela 2 | _ | Parâmetros do circuito.                   | 10 |

## LISTA DE ABREVIATURAS E SIGLAS

- PI Proportional Integral

- IBC Interleaved Boost Converter

- MMP Maximum Power Point

- KCL Kirchhoff's Current Law

- KVL Kirchhoff's Voltage Law

- DSP Digital Signal Processor

- PWM Pulse Width Modulation

# SUMÁRIO

| 1 | INTRODUÇÕA                               | 1  |

|---|------------------------------------------|----|

| 2 | CONVERSOR BOOST INTERLEAVED              | 2  |

| 3 | LINEARIZAÇÃO DO DISPOSITIVO FOTOVOLTAICO | 2  |

| 4 | MODELO EM ESPAÇO DE ESTADOS DO IBC       | 3  |

|   | 4.1 PRIMEIRO SUBINTERVALO                | 4  |

|   | 4.2 SEGUNDO SUBINTERVALO                 | 5  |

|   | 4.2 TERCEIRO SUBINTERVALO                | 6  |

|   | 4.2 QUARTO SUBINTERVALO                  | 6  |

| 5 | MODELO PARA PEQUENOS SINAIS DO IBC       | 6  |

| 6 | ANÁLISE DE CONTROLE DO IBC               | 8  |

| 7 | RESULTADOS SIMULADOS                     | 10 |

| 8 | RESULTADO EXPERIMENTAIS                  | 11 |

| 9 | CONCLUSÃO                                | 13 |

|   | Agradecimentos                           | 13 |

|   | Referencias                              | 13 |

# Model and Design of an Interleaved Boost Converter

Eduardo Felipe Weber · Cassius Rossi de Aguiar

Received: date / Accepted: date

Abstract The aim of this paper is to analyze and design a boost power converter utilizing the interleaved technique, which improves the load transient response, provides better heat dissipation and less stress on the semiconductors. To represent the interleaved boost converter in a mathematical model, its state space representation is used, where the parasitic resistance of the inductors and semiconductors is considered. In this context, the interleaved boost converter is controlled using a cascade structure with the input current on the inductors in the inner loop and the dc-link voltage in the outer loop. After investigating the response of the controllers in the frequency domain, indicating the stability of the system, the converter is validated by simulations and by experimental measurements highlighting the correct operation of the system, reaching the desired voltage with small residual ripple amplitude.

**Keywords** Interleaved Boost Converter  $\cdot$  Power Electronics  $\cdot$  Photovoltaic Energy

### 1 Introduction

The low-voltage renewable energy sources require, usually, the utilization of different topologies of power electronic converters to adjust its output voltage and current. Mostly solar panels operate in medium to low voltage output and require dc/dc boost converters with high voltage gain to be connected to the grid. Taking

E. F. Weber

C. R. Aguiar Federal University of Technology Paraná E-mail: cassiusaguiar@utfpr.edu.br this into consideration, the main factors that affect efficiency and gain are the correct topology and the accounting for parasitic losses as described in (Thao et al., 2012).

A step-up converter, fit for a renewable energy system that needs high voltage gain, is proposed in (Liu et al., 2015). This converter utilizes two switches, one voltage multiplier cell for each arm and three winding coupled inductors. The utilization of two switches reduces the voltage and current stresses on the semiconductors. Another example is the interleaved boost converter with voltage multiplier proposed in (Franco et al., 2003; Gul, 2003), and modeled in (Spiazzi et al., 2012) which brings many advantages like the use of voltage multiplier cells and specifically the interleaved technique.

Among the most know topologies of dc/dc converter, the interleaved technique introduces numerous benefits, like, current sharing between the arms, use of cheaper semiconductor, reduction of the input current ripple (Thounthong et al., 2009; Fekri et al., 2017; Maalandish et al., 2017), reduced inductors, improvement of the converter efficiency and a better thermal distribution (Jang et al., 2013; Cheng et al., 2013; Ang and Oliva, 2010).

Based on the introduced arguments, this work presents a mathematical model, analysis, closed-loop control and simulation of a two-phase interleaved boost converter (IBC) taking into account the parasitic resistances of the passive components and switches. The employment of multiplier cells was not considered once the targeted voltage gain was achieved without their use.

This paper is organized as follows: in Section II the interleaved technique and the proposed IBC are described; in Section III it is shown the procedure of the photovoltaic device linearization; in Section IV the

Federal University of Technology Paraná Tel.: +55-45-999899343 E-mail: eduardoweber@alunos.utfpr.edu.br

state-space model is made by subdividing the full operation cycle into multiple subintervals and analysing each equivalent circuit; then on Section V the average model and small signal analysis is derived; in Section VI it is made the control analysis of the IBC for its utilization on Section VII where the converter is simulated; on section VIII its shown the experimental results; and lastly, Section IX describes the conclusions made from the execution of this project.

#### 2 Interleaved boost converter

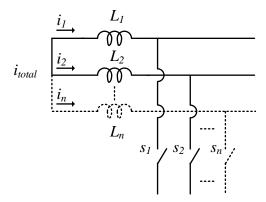

The interleaved technique is the combination of two or more converters in parallel, as shown in Figure (1). The switching of the phases operates in a manner that the current distributes itself between the N phases with a delay of  $360^{\circ}/N$  between each one, thus the resulting switching frequency will be proportional to the number of phases N.

By the fact that the current splits across the arms of the phases, the currents will be reduced in each arm. Therefore, inductors and semiconductors maximum ratings can also be reduced, which implies in better costs. Furthermore, it is possible to arrange the components with better distribution, resulting in more efficient heat dissipation.

**Fig. 1** Representation of an interleaved technique of N phases.

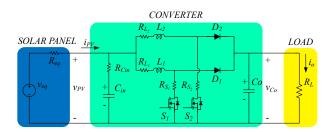

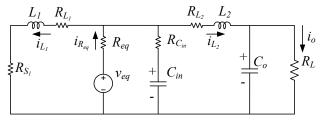

In this project it is developed an interleaved boost converter with two phases, utilizing an arrangement of solar panels as input, using two switches and a load represented as a resistor  $R_L$  (Figure 2). The goal is to develop a IBC that supplies 200 V and up to 1 kW of power.

As stated previously the parasitic losses affect the efficiency of the converter, thus, they shall be accounted in order to be compensated.  $R_{C_{in}}$  is the parasitic resistance of the input capacitor  $C_{in}$ ,  $R_{L_1}$ ,  $R_{L_2}$  the parasitic

resistances of the inductors  $L_1$  and  $L_2$  respectively and, at last, the intrinsic losses  $R_{S_1}$ ,  $R_{S_2}$  from the switches  $S_1$  and  $S_2$ .

Fig. 2 Proposed boost interleaved converter.

In the following sections the development process will be described step by step, starting with the linearization of the simulated arrangement of solar panels, then describing the space-state model, the average model, the small signal analyses to acquire the transfer functions, the control topology and at last the simulation and experimental results.

### 3 Linearization of the photovoltaic device

Instead of utilizing an ideal power source to represent the arrangement of solar panels it is preferable to find an equation that is closer to the operation of a real solar panel (Villalva, 2010). However, the equation that describes a photovoltaic device is not linear. Therefore it is necessary to linearize a point in the curve of current by voltage from the solar panel, thereby, finding an equivalent circuit that can be represented in the model of the system. The chosen point to do it is the point where the solar panel operates with its maximum power (MPP).

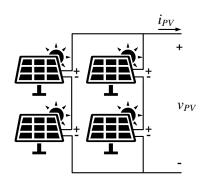

The solar panel that will be simulated in this project is the 280W model CS6K280P from Canadian Solar. It will be arranged using four solar panels, being two in series and this group in parallel with another two in series as shown in the Figure (3).

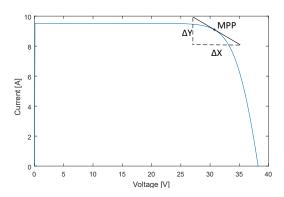

Figure (4) represents the curve of the current by the voltage of one solar panel. The highlighted point is where the solar panel operates at its full capacity, generating its maximum power output. The tangent line over the point defines how the linearization of the curve is made.

The conductance of the panels arrangement g, linearized in the chosen point in the position (X, Y), it is calculated in the equation (1), where (I, V) is a point inside the tangent line.

$$g = \frac{\Delta Y}{\Delta X} = \frac{i_{PV} - I}{v_{PV} - V} = \frac{1}{R_{eq}} \tag{1}$$

Fig. 3 Arrangement of the solar panels.

Fig. 4 Example of curve of the current in function of the voltage of a solar panel.

Rearranging (1) is obtained (2) that represents the linear model of the tangent line on the chosen point.

$$i_{PV} = (-gV + I) + gv_{PV} \tag{2}$$

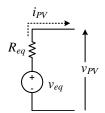

Thereby, it is possible to represent the linearized solar panel as an equivalent circuit as pictured in the Figure (5)

Fig. 5 Equivalent circuit to represent a solar panel.

Analyzing the circuit in the Figure (5), the equations (3) and (4) are obtained representing the equivalent resistance and equivalent voltage of the solar panel respectively.

$$R_{eq} = -\frac{1}{g} \tag{3}$$

$$V_{eq} = V - \frac{I}{g} \tag{4}$$

With this linearized model, the following analysis for the project of controllers will be facilitated and, furthermore, this model describes the operation of the solar panel satisfactorily.

#### 4 IBC state-space model

As the aim of this project is to control the IBC in closedloop, it is necessary to represent it mathematically. To do so, the state-space model was developed in order to describe the IBC. The space-state modeling is based on the works of (Aguiar, 2017) and (Fuzato, 2015).

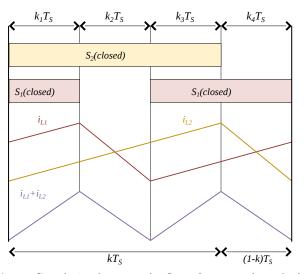

The semiconductors are switching with  $180^{\circ}$  apart, and considering the full period as  $T_s$  and the period that one switch is closed as  $kT_s$  there will be four different subintervals:  $k_1T_s$ , where the switches  $S_1$  and  $S_2$  are closed;  $k_2T_s$ , when the switch  $S_2$  keeps closed and the switch  $S_1$  opens;  $k_3T_s$  when, again, both switches are closed; and lastly,  $k_4T_s$  when the switch  $S_2$  opens and the switch  $S_1$  remains closed.

During the first subinterval both inductors,  $L_1$  and  $L_2$ , are charging. When the subinterval finishes and the second subinterval starts the inductor  $L_1$  discharges its energy on the load  $R_L$ , then on the third interval, the inductor  $L_1$  restart charging, at the same time as  $L_2$ . On the final subinterval, the inductor  $L_2$  discharges its energy on the load  $R_L$ , and the cycle repeats. The Figure (6) represents the correlation between the flow of current through the inductors and the state of the switches.

To obtain the state-space model of the IBC the state vector will be assumed as (5), the input vector as (6), and the output vector as (7).

$$x = \begin{bmatrix} i_{L_1} & i_{L_2} & v_{C_{in}} & v_{Co} \end{bmatrix}^T$$

(5)

$$u = \begin{bmatrix} v_{PV} \\ i_o \end{bmatrix} \tag{6}$$

$$y = \begin{bmatrix} i_{L_1} + i_{L_2} \\ v_{Co} \end{bmatrix} \tag{7}$$

To proceed with the following analysis, such as average model and small-signal analysis, it is necessary to model the equivalent circuit of each subinterval.

Fig. 6 Correlation between the flow of current through the inductors and the state of the switches, adapted from Fuzato (2015)

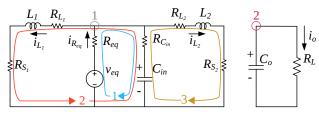

### 4.1 First Subinterval

In the first subinterval, both switches are closed and both diodes are reversely biased, as represented in the Figure (7).

Fig. 7 Equivalent circuit of the first subinterval.

Applying KCL (Kirchhoff's Current Law) on the node (1) in (8) is obtained, and using KVL (Kirchhoff's Voltage Law) on the loop (1) it is possible to obtain the equation (9).

$$i_{L_1} + i_{L_2} + C_{in} \frac{dv_{C_{in}}}{dt} = i_{R_{eq}} \tag{8}$$

$$i_{R_{eq}} = \left[ v_{eq} - (v_{C_{in}} + C_{in} \frac{dv_{C_{in}}}{dt} R_{C_{in}}) \right] \frac{1}{R_{eq}}$$

(9)

Applying (9) in (8), the following equation is obtained:

$$i_{L_{1}} + i_{L_{2}} + C_{in} \frac{dv_{C_{in}}}{dt} = \left(v_{eq} - v_{C_{in}} - C_{in} \frac{dv_{C_{in}}}{dt} R_{C_{in}}\right) \frac{1}{R_{eq}}$$

(10)

Now, isolating  $\frac{dv_{C_{in}}}{dt}$  in the equation (10) it is possible to obtain:

$$\frac{dv_{C_{in}}}{dt} = \frac{-R_{eq}(i_{L_1} + i_{L_2}) + v_{eq} - v_{C_{in}}}{C_{in}(R_{eq} + R_{C_{in}})}$$

(11)

Applying KVL in the loop (2), (12) is obtained. Applying (11) on (12) and isolating  $\frac{di_{L_1}}{dt}$  (13) is obtained.

$$-v_{C_{in}} - R_{C_{in}}C_{in}\frac{dv_{C_{in}}}{dt} + L_1\frac{di_{L_1}}{dt} + i_{L_1}(R_{L_1} + R_{S_1}) = 0$$

(12)

$$\frac{di_{L_1}}{dt} = + v_{C_{in}} \left[ \frac{R_{eq}}{(R_{eq} + R_{C_{in}})L_1} \right] \\

+ v_{eq} \left[ \frac{R_{C_{in}}}{(R_{eq} + R_{C_{in}})L_1} \right] \\

+ i_{L_1} \left[ - \frac{R_{L_1}}{L_1} - \frac{R_{S_1}}{L_1} - \frac{R_{C_{in}}R_{eq}}{(R_{eq} + R_{C_{in}})L_1} \right] \\

+ i_{L_2} \left[ - \frac{R_{C_{in}}R_{eq}}{(R_{eq} + R_{C_{in}})L_1} \right]$$

(13)

Repeating the same process in the loop (3), the following equations are found:

$$-v_{C_{in}} - R_{C_{in}}C_{in}\frac{dv_{C_{in}}}{dt} + L_2\frac{di_{L_2}}{dt} + i_{L_2}(R_{L_2} + R_{S_2}) = 0$$

(14)

$$\frac{di_{L_2}}{dt} = + v_{C_{in}} \left[ \frac{R_{eq}}{(R_{eq} + R_{C_{in}})L_2} \right] \\

+ v_{eq} \left[ \frac{R_{C_{in}}}{(R_{eq} + R_{C_{in}})L_2} \right] \\

+ i_{L_1} \left[ - \frac{R_{C_{in}}R_{eq}}{(R_{eq} + R_{C_{in}})L_2} \right] \\

+ i_{L_2} \left[ - \frac{R_{L_2}}{L_2} - \frac{R_{S_2}}{L_2} - \frac{R_{C_{in}}R_{eq}}{(R_{eq} + R_{C_{in}})L_2} \right]$$

(15)

At last, applying KCL in the node (2) results in the following equation:

$$\frac{dv_{C_o}}{dt} = \frac{v_{C_o}}{R_L C_o} \tag{16}$$

Now with the equations (11), (13), (15), (16) and assuming that  $\alpha = (R_{eq} + R_{C_{in}})$  it is possible to build the matrices  $A_1$  and  $B_1$ , represented by the following equations, respectively on the matrices (18) and (17):

$$A_{1} = \begin{bmatrix} \frac{-R_{L_{1}}\alpha - R_{S_{1}}\alpha - R_{C_{in}}R_{eq}}{\alpha L_{1}} & -\frac{R_{C_{in}}R_{eq}}{\alpha L_{1}} & \frac{R_{eq}}{\alpha L_{1}} & 0\\ -\frac{R_{C_{in}}R_{eq}}{\alpha L_{2}} & \frac{-R_{L_{2}}\alpha - R_{S_{2}}\alpha - R_{C_{in}}R_{eq}}{\alpha L_{2}} & \frac{R_{eq}}{\alpha L_{2}} & 0\\ -\frac{R_{eq}}{C_{in}\alpha} & -\frac{R_{eq}}{C_{in}\alpha} & -\frac{1}{C_{in}\alpha} & 0\\ 0 & 0 & 0 & -\frac{1}{R_{LC_{0}}} \end{bmatrix}$$

(18)

$$\boldsymbol{B_{1}} = \begin{bmatrix} \frac{R_{C_{in}}}{\alpha L_{1}} & 0\\ \frac{R_{C_{in}}}{\alpha L_{2}} & 0\\ \frac{1}{\alpha C_{in}} & 0\\ 0 & 0 \end{bmatrix}$$

(17)

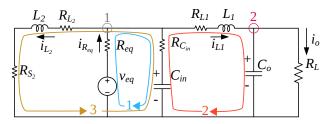

### 4.2 Second Subinterval

In the second subinterval the switch  $S_2$  remains closed, but now the switch  $S_1$  opens and the diode  $D_1$  is directly biased as shown in the equivalent circuit of the Figure (8).

Fig. 8 Equivalent circuit of the second subinterval.

After applying KCL at the node (1) and KVL in the loop (1), relations (19) and (20), are derived. Afterwards, relation (21) is obtained by applying (19) on (20).

$$i_{L_1} + i_{L_2} + C_{in} \frac{dv_{C_{in}}}{dt} = i_{R_{eq}}$$

<sup>(19)</sup>

$$i_{R_{eq}} = \left[ v_{eq} - (v_{C_{in}} + C_{in} \frac{dv_{C_{in}}}{dt} R_{C_{in}}) \right] \frac{1}{R_{eq}}$$

(20)

$$i_{L_{1}} + i_{L_{2}} + C_{in} \frac{dv_{C_{in}}}{dt} = \left(v_{eq} - v_{C_{in}} - C_{in} \frac{dv_{C_{in}}}{dt} R_{C_{in}}\right) \frac{1}{R_{eq}}$$

(21)

Now, (22) is obtained by rearranging (21) and isolating  $\frac{dvC_{in}}{dt}$ :

$$\frac{dv_{C_{in}}}{dt} = \frac{-R_{eq}(i_{L_1} + I_{L_2}) + V_{eq} - v_{C_{in}}}{C_{in}(R_{eq} + R_{C_{in}})}$$

(22)

After applying KVL in the loop (2), relation (23) is derived. Afterwards, relation (24) is obtained by applying (22) on (23) and isolating  $\frac{di_{L_1}}{dt}$ .

$$-v_{C_{in}} - R_{C_{in}}C_{in}\frac{dv_{C_{in}}}{dt} + L_1\frac{di_{L_1}}{dt} + i_{L_1}R_{L_1} + v_{Co} = 0$$

(23)

$$\frac{di_{L_{1}}}{dt} = + v_{C_{in}} \left[ \frac{R_{eq}}{(R_{eq} + R_{C_{in}})L_{1}} \right] \\

+ v_{eq} \left[ \frac{R_{C_{in}}}{(R_{eq} + R_{C_{in}})L_{1}} \right] \\

+ i_{L_{1}} \left[ \frac{-R_{L_{1}}(R_{eq} + R_{C_{in}}) - R_{C_{in}}R_{eq}}{(R_{eq} + R_{C_{in}})L_{1}} \right] \\

+ i_{L_{2}} \left[ \frac{-R_{C_{in}}R_{eq}}{(R_{eq} + R_{C_{in}})L_{1}} \right] + v_{Co} \left[ -\frac{1}{L_{1}} \right]$$

(24)

Repeating this process for the loop (3) it is possible to obtain the following equations:

$$-v_{C_{in}} - R_{C_{in}}C_{in}\frac{dv_{C_{in}}}{dt} + L_2\frac{di_{L_2}}{dt} + i_{L_2}(R_{L_2} + R_{S_2}) = 0$$

(25)

$$\frac{di_{L_2}}{dt} = + v_{C_{in}} \left[ \frac{R_{eq}}{(R_{eq} + R_{C_{in}})L_2} \right] \\

+ v_{eq} \left[ \frac{R_{C_{in}}}{(R_{eq} + R_{C_{in}})L_2} \right] \\

+ i_{L_1} \left[ - \frac{R_{C_{in}}R_{eq}}{(R_{eq} + R_{C_{in}})L_2} \right] \\

+ i_{L_2} \left[ - \frac{R_{L_2}}{L_2} - \frac{R_{S_2}}{L_2} - \frac{C_{in}R_{eq}}{(R_{eq} + R_{C_{in}})L_2} \right]$$

(26)

Now performing KCL at the node (2), the following equation is found:

$$\frac{dv_{Co}}{dt} = \frac{i_{L_1}}{C_o} - \frac{v_{Co}}{R_L C_o} \tag{27}$$

$$\boldsymbol{A_{2}} = \begin{bmatrix} \frac{-R_{L_{1}}\alpha - R_{C_{in}}R_{eq}}{\alpha L_{1}} & \frac{-R_{C_{in}}R_{eq}}{\alpha L_{1}} & \frac{R_{eq}}{\alpha L_{1}} & \frac{-1}{L_{1}} \\ \frac{-R_{eq}R_{C_{in}}}{\alpha L_{2}} & \frac{-(R_{L_{2}}+R_{S_{2}})\alpha - R_{eq}R_{C_{in}}}{\alpha L_{2}} & \frac{R_{eq}}{\alpha L_{2}} & 0 \\ -\frac{R_{eq}}{C_{in}\alpha} & -\frac{R_{eq}}{C_{in}\alpha} & -\frac{1}{C_{in}\alpha} & 0 \\ \frac{1}{C_{O}} & 0 & 0 & -\frac{1}{R_{L_{O}}} \end{bmatrix}$$

$A_2$  and  $B_2$  are obtained at (28) and (29) as result of rearranging (22), (24), (26), and (27) in a matrix form.

$$\boldsymbol{B_{2}} = \begin{bmatrix} \frac{R_{C_{in}}}{\alpha L_{1}} & 0\\ \frac{R_{C_{in}}}{\alpha L_{2}} & 0\\ \frac{1}{\alpha C_{in}} & 0\\ 0 & 0 \end{bmatrix}$$

(29)

#### 4.3 Third Subinterval

In this subinterval both of the switches are closed and both diodes are reverse biased in the same manner they were on the first subinterval, hence it is possible to say that both subintervals are equal. Therefore  $A_1 = A_3$ and  $B_1 = B_3$ .

#### 4.4 Fourth Subinterval

Now the  $S_1$  switch mantains itself closed while the switch  $S_2$  opens and the diode  $D_1$  is directly polarized, as shown in figure (9).

Fig. 9 Equivalent circuit of the fourth subinterval.

This subinterval closely resembles to the second subinterval, however where there is an "1" here on the second subinterval there is an "2" reciprocally. Therefore, it is possible to modify the equations (22), (24), (26), and (27) replacing  $L_1$  for  $L_2$ ,  $S_1$  for  $S_2$  and vice versa. Thus, it is possible to acquire the equations of the fourth subinterval with the same relations aforementioned. The resulting equations are given as follows:

$$\frac{dv_{C_{in}}}{dt} = \frac{-R_{eq}(i_{L_2} + i_{L_1}) + V_{eq} - v_{C_{in}}}{C_{in}(R_{eq} + R_{C_{in}})}$$

(30)

$$\frac{di_{L_2}}{dt} = + v_{C_{in}} \left[ \frac{R_{eq}}{(R_{eq} + R_{C_{in}})L_2} \right] \\

+ v_{eq} \left[ \frac{R_{C_{in}}}{(R_{eq} + R_{C_{in}})L_2} \right] \\

+ i_{L_2} \left[ \frac{-R_{L_2}(R_{eq} + R_{C_{in}}) - R_{C_{in}}R_{eq}}{(R_{eq} + R_{C_{in}})L_2} \right] \\

+ i_{L_1} \left[ \frac{-R_{C_{in}}R_{eq}}{(R_{eq} + R_{C_{in}})L_2} \right] + v_{Co} \left[ -\frac{1}{L_2} \right]$$

(31)

$$\frac{di_{L_1}}{dt} = + v_{C_{in}} \left[ \frac{R_{eq}}{(R_{eq} + R_{C_{in}})L_1} \right] \\

+ v_{eq} \left[ \frac{R_{C_{in}}}{(R_{eq} + R_{C_{in}})L_1} \right] \\

+ i_{L_2} \left[ - \frac{R_{C_{in}}R_{eq}}{(R_{eq} + R_{C_{in}})L_1} \right] \\

+ i_{L_1} \left[ - \frac{R_{L_1}}{L_1} - \frac{R_{S_1}}{L_1} - \frac{C_{in}R_{eq}}{(R_{eq} + R_{C_{in}})L_1} \right]$$

(32)

$$\frac{dv_{Co}}{dt} = \frac{i_{L_2}}{C_o} - \frac{v_{Co}}{R_L C_o} \tag{33}$$

Rearranging the latter equations into a matricial form it is possible to form the matrices represented in (35) and (34).

$$\boldsymbol{B_4} = \begin{bmatrix} \frac{R_{C_{in}}}{\alpha L_1} & 0\\ \frac{R_{C_{in}}}{\alpha L_2} & 0\\ \frac{1}{\alpha C_{in}} & 0\\ 0 & 0 \end{bmatrix}$$

(35)

### 5 IBC small-signal model

In this section the average and small signal models are investigated. The switching intervals of the circuit are defined by the present switches and diodes on the circuit. Every one of the subintervals with its equivalent circuit resultant from the switching was modeled in the former section.

Thus, after acquiring the state-space model matrices of all subintervals, the average matrix that represents the full interval can be found by the combination of

$$\boldsymbol{A_4} = \begin{bmatrix} \frac{-(R_{L_1} + R_{S_1})\alpha - R_{eq}R_{C_{in}}}{\alpha L_1} & \frac{-R_{eq}R_{C_{in}}}{\alpha L_1} & \frac{R_{eq}}{\alpha L_1} & 0\\ \frac{-R_{C_{in}}R_{eq}}{\alpha L_2} & \frac{-R_{L_2}\alpha - R_{C_{in}}R_{eq}}{\alpha L_2} & \frac{R_{eq}}{\alpha L_2} & \frac{-1}{L_2}\\ -\frac{R_{eq}}{C_{in}\alpha} & -\frac{R_{eq}}{C_{in}\alpha} & -\frac{1}{C_{in}\alpha} & 0\\ \frac{1}{C_O} & 0 & 0 & -\frac{1}{R_L C_o} \end{bmatrix}$$

the obtained matrices weighted by its relative period of every one of the switching subintervals, as shown in the subsequent equation:

$$\dot{\boldsymbol{x}} = \left(\sum_{i=1}^{4} \boldsymbol{A}_{i} k_{i}\right) \boldsymbol{x} + \left(\sum_{i=1}^{4} \boldsymbol{B}_{i} k_{i}\right) \boldsymbol{u}$$

(36)

Recalling Figure (6), and observing the switching angle offset of 180 degrees, it is possible to state that  $k_1T_S + k_2T_S = \frac{T_S}{2}$  and that  $k_3T_S + k_4T_S = \frac{T_S}{2}$ . It is also possible to affirm that  $k_2$  and  $k_4$  are equal to (1 - k), once that it is the interval in which every one of the switches remain open. Therefore  $k_1 = k_3 = \frac{1}{2} - (1-k) = k - \frac{1}{2}$ . Thus the equation that describes the full interval of the IBC is:

$$A = \sum_{i=1}^{4} A_i k_i = A_1 (k - \frac{1}{2}) + A_2 (1 - k) + A_3 (k - \frac{1}{2}) + A_4 (1 - k)$$

(37)

$$A = (-A_1 + A_2 + A_4) + k(2A_1 - A_2 - A_4)$$

(38)

As the  $\boldsymbol{B}$  matrices are all equal, its weighted value is invariant:

$$\boldsymbol{B} = \boldsymbol{B}_1 \tag{39}$$

Considering that this converter has an non-linear behaviour and that any perturbance in the input vector  $\boldsymbol{u} = \boldsymbol{U} + \hat{\boldsymbol{u}}$ , where  $\boldsymbol{U}$  is the average dc value and  $\hat{\boldsymbol{u}}$  is the perturbance, will in a similar manner spread to the state vector  $\boldsymbol{x} = \boldsymbol{X} + \hat{\boldsymbol{x}}$  and consequently to the output vector  $\boldsymbol{y} = \boldsymbol{Y} + \hat{\boldsymbol{y}}$ , and thus the duty cycle k will change from cycle to cycle around a linearization point, as represented by  $k = K + \hat{k}$  where K is the average value in steady state and  $\hat{k}$  is perturbance around the linearization point. Without the effect of the perturbance the system can be described as:

$$\dot{x} = Ax + Bu = + [(-A_1 + A_2 + A_4) + k(2A_1 - A_2 - A_4)]x \quad (40) + Bu$$

Inserting the perturbation in (40):

$$\dot{X} + \hat{\hat{x}} = \left[ (-A_1 + A_2 + A_4) + (K + \hat{k})(2A_1 - A_2 - A_4) \right] (X + \hat{x}) + B(U + \hat{u})$$

(41)

Considering steady state, the values from the state variables are constant, and consequently, the state vector derivative is zero. Thus resulting in the following equations:

$$\dot{\boldsymbol{X}} = 0 \tag{42}$$

$$0 = AX + BU \tag{43}$$

$$\boldsymbol{X} = -\boldsymbol{A}^{-1}\boldsymbol{B}\boldsymbol{U} \tag{44}$$

Therefore, it is possible to obtain (45) when considering that the variation of the mean value is null, as shown in (42), and considering that the product of the two perturbations are minute, that is  $\hat{x}\hat{k} \ll 1$ .

$$\hat{\boldsymbol{x}} = \left[ (-\boldsymbol{A_1} + \boldsymbol{A_2} + \boldsymbol{A_4}) + K(2\boldsymbol{A_1} - \boldsymbol{A_2} - \boldsymbol{A_4}) \right] \hat{\boldsymbol{x}} \\

+ (2\boldsymbol{A_1} - \boldsymbol{A_2} - \boldsymbol{A_4}) \boldsymbol{X} \hat{\boldsymbol{k}} + \boldsymbol{B} \hat{\boldsymbol{u}} \qquad (45) \\

= \boldsymbol{A_n} \hat{\boldsymbol{x}} + \boldsymbol{B} \hat{\boldsymbol{u}} + \boldsymbol{F} \hat{\boldsymbol{k}}$$

Assuming  $A_n = [(-A_1 + A_2 + A_4) + K(2A_1 - A_2 - A_4)]$  and  $F = (2A_1 - A_2 - A_4)X$  and also that the AC component of the duty cycle  $\hat{k}$  is a new input of the system it is possible to incorporate it on the input matrix, resulting in a new matrix  $B' = [B \ F]$ , as shown in:

$$\hat{\dot{x}} = A_n + \begin{bmatrix} B & F \end{bmatrix} \begin{bmatrix} \hat{u} \\ \hat{k} \end{bmatrix} = A_n \hat{x} + B' \hat{u}'$$

(46)

Applying the Laplace's Transform in (46) and, regarding its terms, we obtain (47):

(34)

$$\begin{pmatrix}

\hat{\hat{x}} = A_n \hat{x} + B' \hat{u}' \\

s \hat{x} = A_n \hat{x}(s) + B' \hat{u}' \\

\hat{x}(s)(sI - A_n) = B' \hat{u}' \\

\hat{x}(s) = (sI - A_n)^{-1} B' \hat{u}'

\end{cases}$$

(47)

Considering only the transfer functions where the input is the fluctuation of the duty cycle around the linearized point, it is necessary to consider  $\hat{u} = 0$ , thus its found:

$$\hat{\boldsymbol{x}}(\boldsymbol{s}) = (\boldsymbol{s}\boldsymbol{I} - \boldsymbol{A}_{\boldsymbol{n}})^{-1}\boldsymbol{F}\hat{\boldsymbol{k}}$$

(48)

The output voltage, described by (49) and the inductor current, described by (50), are found through the linear combination of the variables of the state vector with output matrix  $C_v$ , (51), and  $C_i$ , (52), with D = 0.

$$\hat{v}_{Co}(s) = \boldsymbol{C}_{\boldsymbol{v}} \hat{\boldsymbol{x}}(\boldsymbol{s}) \tag{49}$$

$$\hat{i}_L(s) = \boldsymbol{C}_{\boldsymbol{i}} \hat{\boldsymbol{x}}(\boldsymbol{s}) \tag{50}$$

$$\boldsymbol{C}_{\boldsymbol{v}} = \begin{bmatrix} 0 & 0 & 1 \end{bmatrix} \tag{51}$$

$$\boldsymbol{C_i} = \begin{bmatrix} 1 & 1 & 0 \end{bmatrix} \tag{52}$$

Thus, it is possible to acquire the output voltage and input current as functions of duty cycle:

$$G_{\boldsymbol{v}}(s) = \frac{\hat{v}_{Co}(s)}{\hat{k}(s)} = \boldsymbol{C}_{\boldsymbol{v}}(s\boldsymbol{I} - \boldsymbol{A}_{\boldsymbol{n}})^{-1}\boldsymbol{F}$$

(53)

$$G_{i}(s) = \frac{\hat{i}_{L}(s)}{\hat{k}(s)} = C_{i}(sI - A_{n})^{-1}F$$

(54)

#### 6 IBC control analysis

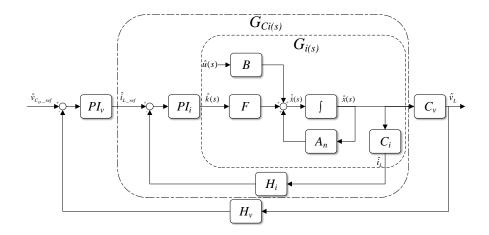

This section presents the control analysis, PI (Proportional Integral) controllers were chosen once its performance was considered satisfactory for the IBC. The selected topology and its analysis are based on the model proposed by (Fuzato et al., 2018) and (Aguiar, 2017) and it is shown in Figure (10).

The first controls the inductors currents  $(PI_i)$  and the second one controls the dc link voltage  $(PI_v)$ , also providing its output as a reference for the first one.

There are several methods to design the controllers of a system. For this project, the Simulink was used in order to compute the controller gains based in the control diagram and in its specified cut frequencies.

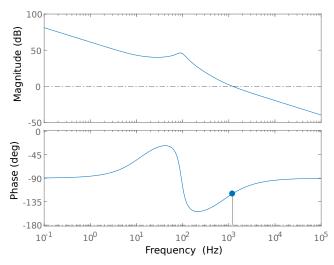

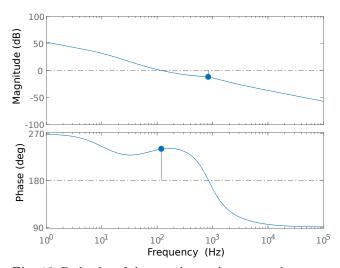

The Figure (11) and (12) show the bode plot with the stability margins of the transfer function in open loop and closed loop as described in the following equations:

$$\hat{d}_L(s) = PI_i(s)\boldsymbol{G}_i(s)\boldsymbol{C}_i\boldsymbol{H}_i \tag{55}$$

$\frac{\hat{i}_L(s)}{\hat{i}_{L,ref}(s)} = \frac{PI_i(s)\boldsymbol{G}_i(s)\boldsymbol{C}_i\boldsymbol{H}_i}{1 + PI_i(s)\boldsymbol{G}_i(s)\boldsymbol{C}_i\boldsymbol{H}_i}$ (56)

Fig. 10 Diagram of the proposed control model for the converter.

Fig. 11 Bode plot of the open loop current control

Fig. 12 Bode plot of the closed loop current control

The inner loop transfer function can be acquired starting in (57), that was taken from analysing the topology. Assuming that the input AC variation be null  $(\hat{\boldsymbol{u}} = 0)$  and applying Laplace, it is found the equation (58).

$$\hat{\dot{x}} = A_n \hat{x} + B \hat{u} - P I_i F H_i C_i \hat{x} + \hat{i}_{L_{-ref}} P I_i F$$

(57)

$$\frac{\hat{\boldsymbol{x}}(\boldsymbol{s})}{\hat{i}_{L_{ref}}(\boldsymbol{s})} = \boldsymbol{G}_{\boldsymbol{C}\boldsymbol{i}}(\boldsymbol{s}) =$$

$$(\boldsymbol{s}\boldsymbol{I} - \boldsymbol{A}_{\boldsymbol{n}} + \boldsymbol{P}\boldsymbol{I}_{\boldsymbol{i}}\boldsymbol{F}\boldsymbol{H}_{\boldsymbol{i}}\boldsymbol{C}_{\boldsymbol{i}})^{-1}\boldsymbol{P}\boldsymbol{I}_{\boldsymbol{i}}\boldsymbol{F}$$

(58)

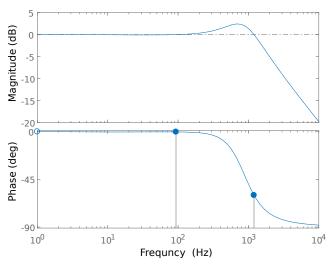

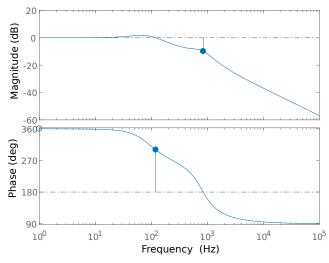

Thus, it is also possible to analyse the frequency response of the controller in open and closed loop in the subsequent figures and equations:

$$\hat{v}_{Co}(s) = H_v P I_v(s) \boldsymbol{C_v} \boldsymbol{G_{Ci}}(s)$$

(59)

$$\frac{\hat{v}_{Co}(s)}{\hat{v}_{C_{o}}_{rst}(s)} = \frac{H_{v}PI_{v}(s)\boldsymbol{C}_{v}\boldsymbol{G}_{Ci}(s)}{1 + H_{v}PI_{v}(s)\boldsymbol{C}_{v}\boldsymbol{G}_{Ci}(s)}$$

(60)

Fig. 13 Bode plot of the open loop voltage control  $\mathbf{Fig.}$

Fig. 14 Bode plot of the closed loop voltage control

The Table 1 specifies the Parameter utilized while performing the control design.

| pecification.         |

|-----------------------|

| Value                 |

| 12.0 kHz              |

| 1.2  kHz              |

| 60°                   |

| $120.0 \ \mathrm{Hz}$ |

| 60°                   |

| 1/32                  |

| 1/400                 |

|                       |

Fig. 16 Current input of the simulated converter.

### 7 Simulated results

The circuit haiming at the validation of the proposed topology and also to demonstrate its effectiveness and robustness. The software *PSIM* is utilized to build the simulation, and is used an DSP (programmed in C), containing the controllers in discrete form with a sampling rate of 12 kHz. The parameters of the circuit are listed in Table 2.

The next figure shows the current ripple on stationary state. It was possible to observe that this ripple does not surpass 6% of the average current value.

Fig. 17 Current input ripple of the simulated converter.

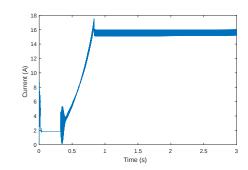

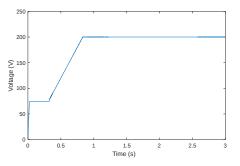

The converter utilizes a soft startup procedure, through a ramp input function. In the following figures, (15) and (16), it is shown the output voltage response of the described startup and the input current respectively, in both figures the ramp initialization function is easily noted.

Fig. 15 The simulated converter.

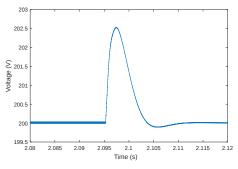

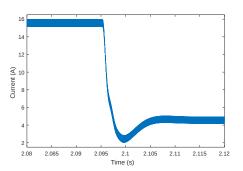

In another instant of the simulation, at 2.095s, the load changes from 1 kW to a third of its value (333 W). The Figure (18) exhibits the output voltage response and the Figure (19) the input current response.

Fig. 18 Output voltage peak on a power drop from 1 kW to 333 W.

Fig. 19 Input current peak on a power drop from 1 kW to 333 W.

Analysing both figures it was possible to observe that the voltage output has an peak of 1.25% while the input current decays 16% before stabilizing.

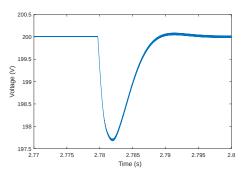

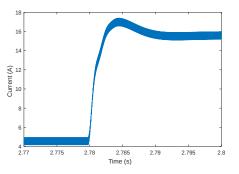

Posteriorly, at the instant 2.780 s, the load changes with a step from 333 W to 1 kW. The following figures displays the output voltage response and the input current response respectively.

Fig. 20 Output voltage peak on a power step from 333 W to 1 kW.

Fig. 21 Input current peak on a power step from 333 W to 1 kW.

Therefore, examining the latter figures, it was possible to observe that the voltage output persists with an error of 1.25% before stabilizing and the current input has an peak of 16% before going back to stabilizing.

#### 8 Experimental results

In order to verify the validity of the IBC, a prototype has been built, Figure (22), to demonstrate the effectiveness of the converter, it uses two switches from the SEMIKRON IGBT Module SK35GD126ET. And the DSP used to control the IBC is the C2000 Delfino MCU F28379D from Texas Instruments.

Fig. 22 Printed circuit board prototype.

Because of the laboratory limitations, such as lack of equipment and tools, the prototype was adjusted to process up to 150 W, supplying 100 V on its output, with a 34 V source on its input. Its controllers and feedback gains from table 1 were also tuned to comply with these adjustments.

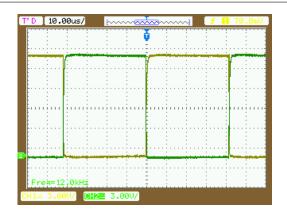

The switches from the IGBT module are operated through the use of PWM (Pulse Width Modulation), which trigger the gate drivers, controling the switches. In the Figure (23) it is shown the waveform for the gate drives used. The PWM frequency is set to 12 kHz.

Fig. 23 Gate drivers waveform.

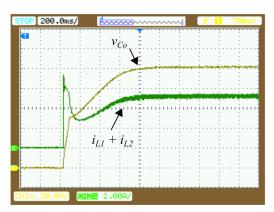

Observing the system initialization, Figure (24), it starts with an soft start utilizing a ramp, the same way as in the simulation (figure 15). Aside from the first peak of current  $(i_{L1}+i_{L2})$ , which is due to the charging of the capacitors, both input current  $(i_{L1}+i_{L2})$  and voltage output  $(v_{C_O})$  have none but a small overshoot, not even reaching 1%.

Fig. 24 Prototype initialization.

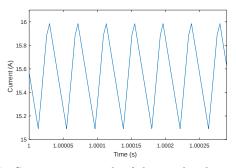

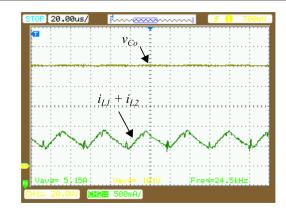

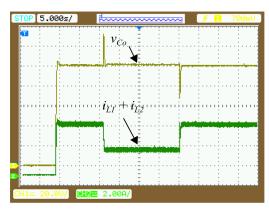

After the initialization the system goes into stationary state, figure (25), the output voltage  $(v_{C_O})$  shows the effectiveness of the controller as its level is fixed on its designed value having a voltage gain of 2.94. While the input current has a small ripple of less than 4%. Note that, even though the switches operate in 12 kHz the input current  $(i_{L1}+i_{L2})$  has a rate of 24 kHz, which is due to the benefit of using the interleaved technique.

Fig. 25 Prototype stationary state.

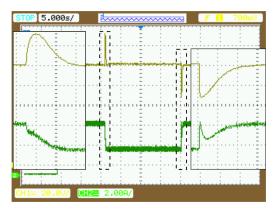

In the scenario shown in figure (26), first, the system initializes with a full load and, later on, the load decreases by 50%. Lastly, the load is again increased to 100%.

Fig. 26 Response from instant power change.

Going in more detail about this last event, figure (27) shows an image focusing on the instant that the load power drops and the instant that the load goes back to its full value. It is possible to observe that the input current  $(i_{L1} + i_{L2})$  shows no overshoot when the load power drops, but display a peak when there is an instant step of power. While the output voltage  $(v_{Co})$  shows high spikes, in this case of approximately 25%, when any considerably high instant power change happens to the load.

Fig. 27 Response from instant power change detailed.

### 9 Conclusion

This work presented a two-phase boost interleaved converter, its equations, analysis and control design. Reducing the stress on the semiconductors by the utilization of the interleaved technique as its main feature, a very important factor when utilized on grid-connected systems and uninterruptible applications.

Other important characteristics of the proposed converter are reduced input current ripple, high switching frequency, simple control system, as it uses classical PI controllers.

In contrast, the principal drawbacks of the proposed converter is its duty cycle limitation, it must not be lower than 50%. The converter also requires a soft start and also the current control could be improved to soften its overshoots. There are also some issues with the experimental prototype, principally the high output voltage peak on instant power changes.

Lastly, the proposed converter showed its effectiveness through simulation and experimentation. Still, for future work, it is planned to model parasitic resistances that were ignored and experiment with different kinds of control, such as Fuzzy, to improve its performance.

Acknowledgements The authors would like to thank the Institution UTFPR-TD for the permission to use its facilities, equipment, tools and for the monetary support through the NOTICE 1/2019 - PROREC/PROGRAD "APOIO A EXE-CUCAO DE TRABALHOS DE CONCLUSAO DE CURSOS – TCC". Thanks also to Fundação Araucária for its funding.

### References

#### (2003) DOI 10.1109/isie.2003.1267284

Aguiar CRd (2017) Contribuição ao gerenciamento e controle de células a combustível e armazenadores de energia para a operação em geração distribuída. PhD thesis, DOI 10.11606/T.18.2017.tde-09112017-103011, URL http://www.teses.usp.br/teses/disponiveis/18/18153/tde-

Ang S, Oliva A (2010) Power-Switching Converters. CRC Press

09112017-103011/

- Cheng SJ, Lo YK, Chiu HJ, Kuo SW (2013) High-efficiency digital-controlled interleaved power converter for high-power PEM fuel-cell applications. IEEE Transactions on Industrial Electronics 60(2):773–780, DOI 10.1109/tie.2012.2206349, URL https://doi.org/10.1109/tie.2012.2206349

- Fekri M, Molavi N, Adib E, Farzanehfard H (2017) High voltage gain interleaved DC–DC converter with minimum current ripple. IET Power Electronics 10(14):1924–1931, DOI 10.1049/iet-pel.2016.0675, URL https://doi.org/10.1049%2Fiet-pel.2016.0675

- Franco L, Pfitscher L, Gules R (2003) A new high static gain nonisolated DC-DC converter. In: IEEE 34th Annual Conference on Power Electronics Specialist, 2003. PESC 03., IEEE, DOI 10.1109/pesc.2003.1216786, URL https://doi.org/10.1109%2Fpesc.2003.1216786

- Fuzato GH, Aguiar CR, Bastos RF, Machado RQ (2018) Evaluation of an interleaved boost converter powered by fuel cells and connected to the grid via voltage source inverter. IET Power Electronics 11(10):1661–1672, DOI 10.1049/iet-pel.2017.0788, URL https://doi.org/10.1049/iet-pel.2017.0788

- Fuzato GHF (2015) Análise de um conversor boost interleaved com multiplicador de tensão para sistemas de geração distribuída que utilizam células a combustível como fonte primária

- М, Ciobotaru M, Agelidis VG (2013)Jang single-phase grid-connected А fuel  $\operatorname{cell}$ system based on a boost-inverter. IEEE Transactions on Power Electronics 28(1):279-288,DOI 10.1109/tpel.2012.2199770, URL https://doi.org/10.1109/tpel.2012.2199770

- Liu H, Li F, Ai J (2015) A novel high stepup dual switches converter with coupled inductor and voltage multiplier cell for a renewable energy system. IEEE Transactions on Power Electronics pp 1–1, DOI 10.1109/tpel.2015.2478809, URL https://doi.org/10.1109%2Ftpel.2015.2478809

- Maalandish M, Hosseini SH, Ghasemzadeh S, Babaei E, Alishah RS, Jalilzadeh T (2017) Six-phase interleaved boost dc/dc converter with high-voltage gain and reduced voltage stress. IET Power Electronics 10(14):1904–1914, DOI 10.1049/iet-pel.2016.1029, URL https://doi.org/10.1049%2Fiet-pel.2016.1029

- Spiazzi G, Buso S, Sichirollo F, Corradini L (2012) Small-signal modeling of the interleaved boost

with voltage multiplier. In: 2012 IEEE Energy Conversion Congress and Exposition (ECCE), IEEE, DOI 10.1109/ecce.2012.6342789, URL https://doi.org/10.1109%2Fecce.2012.6342789

- Thao NM, Thang TV, Ganeshkumar P, Park JH (2012) Steady-state analysis of the boost converter for renewable energy systems. In: Proceedings of The 7th International Power Electronics and Motion Control Conference, IEEE, DOI 10.1109/ipemc.2012.6258883, URL https://doi.org/10.1109%2Fipemc.2012.6258883

- Thounthong P, Sethakul P, Rael S, Davat B (2009) Fuel cell current ripple mitigation by interleaved technique for high power applications. In: 2009 IEEE Industry Applications Society Annual Meeting, IEEE, DOI 10.1109/ias.2009.5324897, URL https://doi.org/10.1109%2Fias.2009.5324897

- Villalva MG (2010) Conversor eletrônico de potência trifásico para sistema fotovoltaico conectado à rede elétrica. PhD thesis, UNICAMP, Campinas - SP