## Object Tracking Using a Many-Core Embedded System

### Laercio Minozzo

Dissertação apresentada à Escola Superior de Tecnologia e de Gestão de Bragança para obtenção do Grau de Mestre em Sistemas de Informação.

Trabalho orientado por: José Rufino, José Lima Paulo Lopes de Menezes, Arnaldo Cândido Jr.

Esta dissertação não inclui as críticas e sugestões feitas pelo Júri.

Bragança

2017

## Object Tracking Using a Many-Core Embedded System

### Laercio Minozzo

Dissertação apresentada à Escola Superior de Tecnologia e de Gestão de Bragança para obtenção do Grau de Mestre em Sistemas de Informação.

Trabalho orientado por: José Rufino, José Lima Paulo Lopes de Menezes, Arnaldo Cândido Jr.

Esta dissertação não inclui as críticas e sugestões feitas pelo Júri.

Bragança

2017

### Abstract

Object localization and tracking is essential for many practical applications, such as mancomputer interaction, security and surveillance, robot competitions, and Industry 4.0. Because of the large amount of data present in an image, and the algorithmic complexity involved, this task can be computationally demanding, mainly for traditional embedded systems, due to their processing and storage limitations. This calls for investigation and experimentation with new approaches, as emergent heterogeneous embedded systems, that promise higher performance, without compromising energy efficiency.

This work explores several real-time color-based object tracking techniques, applied to images supplied by a RGB-D sensor attached to different embedded platforms. The main motivation was to explore an heterogeneous Parallella board with a 16-core Epiphany coprocessor, to reduce image processing time. Another goal was to confront this platform with more conventional embedded systems, namely the popular Raspberry Pi family. In this regard, several processing options were pursued, from low-level implementations specially tailored to the Parallella, to higher-level multi-platform approaches.

The results achieved allow to conclude that the programming effort required to efficiently use the Epiphany co-processor is considerable. Also, for the selected case study, the performance attained was below the one offered by simpler approaches running on quad-core Raspberry Pi boards.

### Resumo

A localização e o seguimento de objetos são essenciais para muitas aplicações práticas, como interação homem-computador, segurança e vigilância, competições de robôs e Indústria 4.0. Devido à grande quantidade de dados presentes numa imagem, e à complexidade algorítmica envolvida, esta tarefa pode ser computacionalmente exigente, principalmente para os sistemas embebidos tradicionais, devido às suas limitações de processamento e armazenamento. Desta forma, é importante a investigação e experimentação com novas abordagens, tais como sistemas embebidos heterogéneos emergentes, que trazem consigo a promessa de melhor desempenho, sem comprometer a eficiência energética.

Este trabalho explora várias técnicas de seguimento de objetos em tempo real baseado em imagens a cores adquiridas por um sensor RBD-D, conectado a diferentes sistemas embebidos. A motivação principal foi a exploração de uma placa heterogénea Parallella com um co-processador Epiphany de 16 núcleos, a fim de reduzir o tempo de processamento das imagens. Outro objetivo era confrontar esta plataforma com sistemas embebidos mais convencionais, nomeadamente a popular família Raspberry Pi. Nesse sentido, foram prosseguidas diversas opções de processamento, desde implementações de baixo nível, específicas da placa Parallella, até abordagens multi-plataforma de mais alto nível.

Os resultados alcançados permitem concluir que o esforço de programação necessário para utilizar eficientemente o co-processador Epiphany é considerável. Adicionalmente, para o caso de estudo deste trabalho, o desempenho alcançado fica aquém do conseguido por abordagens mais simples executando em sistemas Raspberry Pi com quatro núcleos.

## Acknowledgments

I am grateful to Professors José Rufino, José Lima, Paulo Lopes de Menezes, and Arnaldo Cândido Jr. for the guidance, dedication, patience, availability and support they have always shown during this work.

I also thank the various people involved in the double diploma program. Without them this work would not be possible. I would therefore like to express my gratitude to all those who, directly or indirectly, contributed to making this a reality.

Finally, I would like to thank all those who, in one way or another, have made it possible to carry out this dissertation.

viii

# Contents

| A        | bstra | $\mathbf{ct}$                   | $\mathbf{v}$ |

|----------|-------|---------------------------------|--------------|

| R        | esum  | 0                               | vi           |

| A        | cknov | wledgments                      | vii          |

| 1        | Intr  | oduction                        | 1            |

| <b>2</b> | Bac   | kground and Tools               | 3            |

|          | 2.1   | Object tracking                 | 3            |

|          | 2.2   | Heterogeneous Embedded Systems  | 4            |

|          | 2.3   | The Parallella Board            | 5            |

|          |       | 2.3.1 Hardware and Architecture | 5            |

|          |       | 2.3.2 Application Development   | 8            |

|          |       | 2.3.3 Use Cases                 | 10           |

|          | 2.4   | The Raspberry Pi family of SBCs | 11           |

|          | 2.5   | RGB-D Sensor                    | 12           |

|          |       | 2.5.1 libfreenect               | 13           |

|          | 2.6   | Profiling Tools                 | 14           |

|          |       | 2.6.1 Valgrind                  | 14           |

|          |       | 2.6.2 Gprof                     | 15           |

|          | 2.7   | Robot Operating System          | 16           |

| 3 | Ger | ieral S | tructure and Initial Version                    | 17 |

|---|-----|---------|-------------------------------------------------|----|

|   | 3.1 | Main    | Components and Stages                           | 17 |

|   |     | 3.1.1   | Concurrent Processing with Pthreads             | 18 |

|   |     | 3.1.2   | Frame Capture                                   | 18 |

|   |     | 3.1.3   | Calibration                                     | 19 |

|   |     | 3.1.4   | Frame Processing                                | 20 |

|   |     | 3.1.5   | Signal Handlers                                 | 22 |

|   | 3.2 | Initial | PThreads Version                                | 23 |

|   |     | 3.2.1   | Frame Capture                                   | 23 |

|   |     | 3.2.2   | Calibration                                     | 24 |

|   |     | 3.2.3   | RGB Frame Binarization                          | 26 |

|   |     | 3.2.4   | Preliminary Evaluation                          | 27 |

| 4 | Opt | imized  | l and Hybrid Versions                           | 31 |

|   | 4.1 | Optim   | nized PThreads Version                          | 31 |

|   |     | 4.1.1   | Frame Capture                                   | 32 |

|   |     | 4.1.2   | Calibration                                     | 33 |

|   |     | 4.1.3   | RGB Frame Compression                           | 33 |

|   |     | 4.1.4   | RGB Frame Binarization                          | 35 |

|   |     | 4.1.5   | Preliminary Evaluation                          | 36 |

|   | 4.2 | Parall  | el Processing with OpenMP                       | 37 |

|   |     | 4.2.1   | Host-only OpenMP                                | 37 |

|   |     | 4.2.2   | Epiphany-specific OpenMP                        | 38 |

|   | 4.3 | Parall  | el Processing with the Epiphany SDK             | 39 |

|   |     | 4.3.1   | Data Exchange via Shared Memory                 | 41 |

|   |     | 4.3.2   | Direct Access to Local Memory                   | 45 |

|   |     | 4.3.3   | Evaluation of Data Exchange Strategies          | 46 |

|   | 4.4 | Parall  | el Processing with OpenMP and the Epiphany eSDK | 47 |

|   | 4.5 | Final   | Evaluation                                      | 47 |

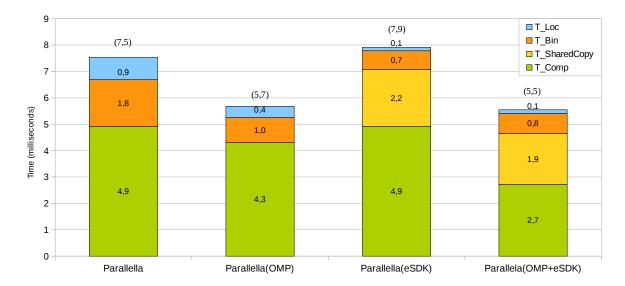

|   | 4.5.1       | Optimized and Hybrid Approaches       | 47 |

|---|-------------|---------------------------------------|----|

|   | 4.5.2       | Comparison with the Raspberry-Pi SBCs | 50 |

| 5 | Conclusio   | ns and Future Work                    | 53 |

| B | ibliography |                                       | 55 |

xii

# List of Tables

| 2.1 | eNone Local Memory Map [Ada13a]                                                  | 7  |

|-----|----------------------------------------------------------------------------------|----|

| 2.2 | Prefix table for eCores remote memory addresses                                  | 7  |

| 2.3 | Microsoft Kinect specifications (version 1)                                      | 13 |

| 3.1 | POSIX Signals captured by the application and actions triggered                  | 22 |

| 4.1 | Characteristics of the tracking application versions on the Parallella platform. | 48 |

| 4.2 | Characteristics of the testing scenarios on the Raspberry Pi platform            | 51 |

# List of Figures

| 2.1  | Parallella board.                                                 | 6  |

|------|-------------------------------------------------------------------|----|

| 2.2  | Main Raspberry Pi models                                          | 12 |

| 2.3  | Microsoft Kinect                                                  | 13 |

| 3.1  | General Structure of the Tracking Application                     | 17 |

| 3.2  | Frame transfer from $t_K$ to $t_P$ (general view)                 | 19 |

| 3.3  | Initial RGB Calibration.                                          | 20 |

| 3.4  | Binarization Process (before and after)                           | 21 |

| 3.5  | Representation of Object Position.                                | 21 |

| 3.6  | Output of the Signal 10                                           | 22 |

| 3.7  | Frame transfer from $t_K$ to $t_P$ (initial version: by copy)     | 24 |

| 3.8  | Internal structure of the colorID data type                       | 25 |

| 3.9  | RGB colour space                                                  | 25 |

| 3.10 | Frame processing time in the initial version (ms).                | 29 |

| 4.1  | General Structure of the Optimized Version.                       | 32 |

| 4.2  | RGB-bitmap calibration data structure                             | 34 |

| 4.3  | First phase of the RGB Frame Compression: Pixel Averaging         | 34 |

| 4.4  | Frame Compression Process (before and after)                      | 35 |

| 4.5  | Frame processing time (ms): initial vs optimized Pthreads version | 36 |

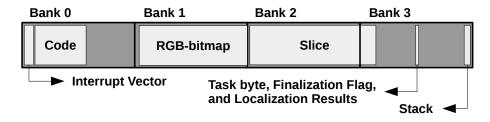

| 4.6  | eCore local memory map when using DMA                             | 44 |

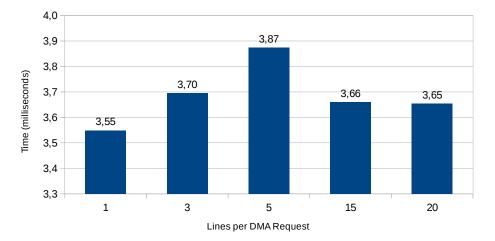

| 4.7  | Number of lines per DMA transfer: impact on Binarization times    | 44 |

| 4.8  | eCore local memory map when using direct access to local memory   | 45 |

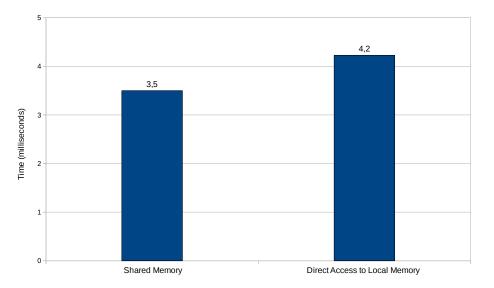

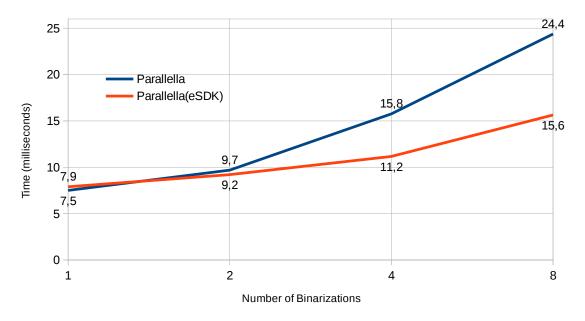

| 4.9  | Binarization time per frame: impact of data exchange strategy 4              |    |  |

|------|------------------------------------------------------------------------------|----|--|

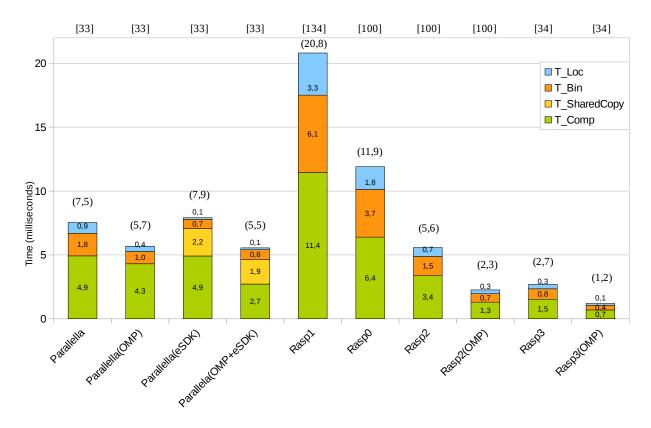

| 4.10 | Parallella Versions Evaluation: (frame processing times), and decomposed     |    |  |

|      | frame processing times; times are averages, in milliseconds (ms). $\ldots$ . | 49 |  |

| 4.11 | Binarization times when computing load increases.                            | 50 |  |

| 4.12 | Multi-platform Results: [frame capture times], (frame processing times),     |    |  |

|      | and decomposed frame processing times; all times are averages, in millisec-  |    |  |

|      | onds (ms).                                                                   | 52 |  |

## Chapter 1

## Introduction

Object localization and tracking is a crucial task in several real-world domains, as augmented reality, human-computer interaction, security and surveillance, robot competitions and aerial vehicles, and Industry 4.0 [iS17], to name a few. The later, for instance, demands the collaboration between robots and humans; in this context, *perception* is one of the most important capabilities, that should be applied as fast as possible to guarantee expected/bounded reaction times.

One of the possible tasks to realize through a computer vision system is to recognize objects automatically. However, this task is not trivial, especially in the treatment of complex scenes, with variations in lighting, position, angle, scale, texture, shadows, deformations, occlusions and other characteristics. To address these issues, efforts are being made not only for image processing and computer vision, but also for areas such as pattern recognition, artificial intelligence, psychophysics, and cognitive sciences [CdFC95].

The growth of the processing capacity of embedded systems, and the parallel processing abilities of many modern Systems-on-Chip (SoCs), are playing an important role in real-time object localization and tracking, addressing more sophisticated image processing techniques, that are able to exploit the extra processing power available. In this regard, a recent trend is the emergence of energy efficient embedded heterogeneous systems, with powerful co-processors that may be used as accelerators in co-operation with their host. This work documents the investigation, development and experimentation conducted on the use of a Parallella heterogeneous embedded system, connected to a Kinect sensor, in order to perform object tracking. It explores a simple technique (color segmentation), through several programming models (including hybrid programming), to take advantage of the concurrent/parallel computing capabilities of the Parallella host and its Epiphany co-processor. Furthermore, the portable nature of some of the developed approaches allowed its deployment and evaluation in several Raspberry Pi models. The ensuing comparison between the Parallela and the Raspberry Pi platforms allowed to derive important conclusions on the cost/benefit ratio of the most performant approaches in each platform.

After the introduction, this document is structured as follows:

- chapter 2 provides background information about object tracking, and on the hardware (embedded systems and RGB-D sensor) and software development tools used;

- chapter 3 starts with a high-level description of the tracking application; it then introduces an initial Pthreads version, along with a first round of evaluations and optimizations, paving the way for further enhancements (presented in chapter 4);

- chapter 4 enhances the initial application version, in the storage and computing domains; the resulting optimized Pthreads version becomes the foundation for hybrid versions, combining Pthreads with OpenMP, and/or with a low-level Parallella framework; intermediate evaluations supporting the choice of different implementation options are presented; the chapter ends with evaluation results from the final versions developed, deployed in the Parallella and in some Raspberry Pi models;

- chapter 5 concludes the document and points directions for future work.

## Chapter 2

## **Background and Tools**

This chapter introduces the background concepts and technological tools pertaining to this work. Specifically, these include concepts on object tracking and a presentation of the hardware platforms and software tools used.

### 2.1 Object tracking

In the context of this work, tracking can be defined as "the problem of estimating the trajectory of an object in an image" [AOM06]. There are several algorithms, applications and systems that solve the object tracking problem. These approaches depend on the object characteristics and features such as appearance, shape, context/environment or scenario, and the end use.

A well known target for object tracking is surveillance (human body tracking). In some of the works that address this topic [AC97, Gav99, MG01], human kinematics provide the basis for implementation, namely using articulated object models. Another object tracking end use is the learning of different views of an object, by training a set of classifiers, like support vector machines [Avi04] or Bayesian networks [PA04].

Object tracking can also be found in such different areas as industrial applications or robotics soccer. Specific examples include manipulators finding objects to perform pick and place operations (helping users in a collaborative task), or mobile soccer robots finding the ball and estimating its position.

Feature selection is the most critical role in tracking. The most desirable property of a visual feature is its uniqueness so that the objects can easily be distinguished in the environment. Feature selection provides a way to perform the image segmentation. This can be achieved using Mean-shift [CM99], Graph-cut [SM00] and Active Contours [CKS95]. Another approach is to use the colour (RGB or HSV) as a feature for histogrambased appearance representations, while for contour-based representation object edges are usually used as features. In general, many tracking algorithms use a combination of these features [Pas01].

Ready to use algorithms/routines can be found in well-known development platforms and frameworks. Mathworks' Matlab includes the Computer Vision System Toolbox, providing video tracking routines that can be used for tracking single or multiple objects. Matlab, however, runs only on x\_86 platforms and is currently restricted to 64 bit running environments [Mat17], which prevents its use on most embedded systems, including the ones used in this work. OpenCV [Ope17a] also offers an API that performs object tracking [Ope17b]. However, this work did not use such API, due to the need of fine-grain control on the code, for parallelization purposes (OpenCV was still used, though for different tasks, like calibration, visualization and to support some data types).

### 2.2 Heterogeneous Embedded Systems

In recent years, advancements in embedded systems and, in particular, the emergence of Systems on Chip (SoC) (mostly propelled by the widespread adoption of mobile devices and the emergence of the Internet-of-Things), brought with it a growing processing capacity, coupled with low/modest power requirements. Nowadays, there is a plethora of small single-board computers (SBCs) [bd17], built around these SoCs. They are usually open-platforms, running an open-source operating system (typically some distribution of Linux) which, coupled with standard development tools, offer tremendous flexibility, at a relatively low cost. In this regard, the Raspberry Pi [Fou17b] line of SBCs is perhaps the most well-established on the market and academia [Bro17], with an enormous ecosystem, ranging from industrial to educational and I&D scenarios.

Virtually all modern SBCs include a multi-core CPU, and the same happens with the Raspberry Pi, since the launch of the 4-core Raspberry Pi 2, in early 2015. Therefore, there has been an increasing interest in exploring the parallel computing capabilities of modern SBCs, to accelerate processing on demanding applications, including object tracking [INA<sup>+</sup>16, TK17]. This trend also extends to heterogeneous embedded systems [KA11], where the main/host processor co-exists with additional devices, of a different architecture, that may be used to execute/accelerate tasks on its behalf. A common example of this is the presence of increasingly powerful Graphical Processing Units (GPUs) in SBCs, usable as numerical co-processors, beyond their native graphical capabilities [NVI]. Another example is provided by the Parallella board [ONUA14, L.11] – the main focus of this work –, coupling a 2-core ARM CPU with a grid of 16 (or more) Epiphany CPUs [Ada13a].

### 2.3 The Parallella Board

Parallella is a credit card sized, single-board computer (Figure 2.1) developed by Adapteva, running on Linux (Ubuntu-based). The intent behind its inception was to have high processing capabilities with low power consumption [ONUA14, L.11]. It was made available to general public in late 2013, after successful Kickstarter funding in 2012. There are several models currently available [Para], all offering an Epiphany III MIMD co-processor. This work explores the "Parallella-16 Desktop Computer", with USB 2.0 data ports (as required, to connect a Kinect sensor), and a micro-HDMI port (for visualization).

#### 2.3.1 Hardware and Architecture

The Parallella board is a heterogeneous system, with processing elements based on two different architectures. The host component consumes up to 5W, and includes a 32 bit dual-core 667 MHz ARMv7 A9 microprocessor, serviced by 1 GByte of SDRAM.

Figure 2.1: Parallella board.

The co-processor consumes an additional 2W, and consists of a 16-core 2D-grid of 32 bit RISC CPUs, based on the Epiphany III architecture [Ada13a]. All Epiphany RISC cores (eCores or eNodes) interconnect through a Network-on-Chip (eMesh), that provides message passing. eCores run at 600 MHz, with 19.2 GFLOPS aggregated single-precision peak performance (2.74 GFLOPS/W, onve host and co-processor consume up to 7W).

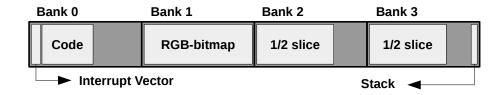

The memory architecture of the Epiphany co-processor does not have an explicit hierarchy and has no caches; it is a distributed shared memory, with a partitioned global address space of 512 KBytes. Each eCore is assigned 32 KBytes of local memory (4 banks of 8 KBytes), for code, stack and data. Table 2.1 shows the memory map of an eCore's local memory space. Besides the four banks of 8 KBytes, it includes other slots reserved in the address space for register access and future expansion.

Fast inter-eCore local memory access is supported: an eCore may directly access the memory of another eCore using the eMesh Network-on-Chip. In order to do so, it is necessary to prefix the desired memory location with the ID of the target eCore in the eMesh Network-on-Chip. That ID is formed by concatenating two tags that depend on the coordinates of the eCore in the eMesh. Table 2.2 shows the 2D coordinates of each eCore (inside the table), and the corresponding tags (leftest column, and topmost line).

| Description                          | Start Address | End Address         | Size    |

|--------------------------------------|---------------|---------------------|---------|

| Interrupt Vector Table               | 0x00000       | 0x0003F             | 64B     |

| Bank 0                               | 0x00040       | 0x01FFF             | 8KB-64B |

| Bank 1                               | 0x02000       | 0x03FFF             | 8KB     |

| Bank 2                               | 0x04000       | 0x05FFF             | 8KB     |

| Bank 3                               | 0x06000       | 0x07FFF             | 8KB     |

| Reserved for future memory expansion | 0x08000       | $0 \mathrm{xEFFFF}$ | N/A     |

| Memory Mapped Registers              | 0xF0000       | $0 \mathrm{xF07FF}$ | 2048B   |

| Reserved                             | 0xF0800       | 0xFFFFF             | N/A     |

Table 2.1: eNone Local Memory Map [Ada13a]

For instance, to access memory location 0x2000 of the eCore (0,1), the address to target would be 0x80902000.

|    | 80    | 90    | A0    | B0    |

|----|-------|-------|-------|-------|

| 80 | (0,0) | (0,1) | (0,2) | (0,3) |

| 84 | (1,0) | (1,1) | (1,2) | (1,3) |

| 88 | (2,0) | (2,1) | (2,2) | (2,3) |

| 89 | (3,0) | (3,1) | (3,2) | (3,3) |

Table 2.2: Prefix table for eCores remote memory addresses.

Buffers shared between the host and the eCores may be created in a 32 MBytes region (8 MBytes usable) of the host main memory, perceived by eCores as an external memory. These buffers may be used for the host and eCores to exchange data and synchronize (or only by eCores to directly store and manage private data), but access to this buffers is slow (even for the host), compared with inter-eCore local memory access. The host can also access directly the local memory of every eCore, but this is slower than access to the shared memory.

Each eCore contains two DMA general purpose channels to simplify data transfers to/from other eCores or shared memory. The DMA engine works at the same frequency as the eCore RISC CPU and can transfer 64-bits per clock cycle.

The two DMA channels have a 2D DMA mechanism that adds some flexibility to transfer data. This mechanism allows the data to be rearranged at the destination during

the data copy by the DMA mechanism, depending on the configuration of some parameters in registers. This mechanism is implemented in hardware, but its operation can be represented by the pseudo-code in listing 2.1.

Listing 2.1: 2D DMA data transfer

```

for(int i=0;i<OUT_COUNTER;i++){</pre>

1

\mathbf{2}

for(int j=0;j<IN_COUNTER;j++){</pre>

3

*dst=*src;

4

dst+=IN_DST_STRIDE;

5

src+=IN_SRC_STRIDE;

\mathbf{6}

}

7

dst+=OUT_DST_STRIDE;

8

src+=OUT_SRC_STRIDE;

9

}

```

The OUT\_COUNTER, IN\_COUNTER, IN\_DST\_STRIDE, IN\_SRC\_STRIDE, OUT\_DST\_STRIDE, and OUT\_SRC\_STRIDE represent the parameters that must be configured in special registers before the start of a DMA transaction. The **src** pointer holds the address of the source memory region and the **dst** pointer holds the address of the destiny memory region. This mechanism can transfer 8, 16, 32 or 64 bits for each cycle, needing to align the steps with the size used through the configuration of the parameters mentioned above.

Finally, it is possible to connect several Parallella boards in a cluster (aiming at performance gains), whether by using a fast inter-chip "eMesh" interconnect (that extends the logical grid of Epiphany cores), or the on-board 1Gbps Ethernet port (for a more traditional cluster configuration). This work used a single board, postponing the exploration of those configurations for future work.

#### 2.3.2 Application Development

Applications that take advantage of the Epiphany device may be developed using the lowlevel Epiphany Software Development Kit [Ada13b], or higher-level frameworks [Parb].

#### **Epiphany Software Development Kit**

The Epiphany Software Development Kit (eSDK) is a set of tools to assist in software development on the Parallella board. The eSDK is based on standard development tools

including an optimizing C-compiler, functional simulator, and debugger. The Epiphany C-Compiler is based on GNU/GCC, and the programs are written in ANSI-C and C++ (partial support), not requiring any language extensions. The eSDK also includes two important libraries: the Epiphany Hardware Abstraction Layer (eHAL) and the Hardware Utility Library (eLib). These two libraries provide a set of routines and data structures necessary to the development of C-based applications.

**Epiphany Hardware Abstraction Layer** The eHAL is a C-library that provides functionality of the Epiphany chip to the host side. The library interface is defined in the *e-hal.h* header file. This library manages the Epiphany chip based on the supplied hardware description file (HDF), which contains all the information about the Epiphany platform, such as chip arrangement, memory locations and defined sizes. This way, an application can easily be migrated between different Epiphany chips. This file is loaded on the initialization function to get the actual Epiphany chip attributes. The Epiphany chip attributes can be retrieved after with some API functions.

During program execution the application can allocate space in the shared memory. This space is defined from the beginning of the shared memory, and the eHAL provides functions to allocate, write, read and free external memory buffers. After an allocation in shared memory, the program can write and read data in allocated space only with special functions provided by the library. The same functions that access the shared memory can also access the local memory of every Epiphany eCores (a write operation is only possible if the eCore involved is idle; to ensure that eCores are idle at the beginning of program execution, it is necessary a reset operation after the initialization operation).

Hardware Utility Library The eLib is the C-library that provides functionality and hardware abstraction in the Epiphany eCores side. The eLib provides essential Epiphany architecture tasks that are not present in standard C and C++. These tasks are as follows: system register functions that allow write and read information of all eCore registers; the interrupt service functions, that are used to attach or detach interrupt-handlers; timer

functions, that allow to set/get the timers values beside starting and stopping the two timers systems; DMA functions, that allow to control the DMA data transfer system; mutex system functions, that allow exclusive access of a single eCore to a shared resource, as well as a barrier function for synchronization between eCores program execution; coreId and work groups functions, allowing the programmer access to IDs and coordinates.

#### **High-Level Approaches**

Higher-level approaches and frameworks to explore the Epiphany accelerator include, among others, i) ePython [Bro16] (for Python-based parallel programming), ii) OpenSH-MEM [RR16] (particularly suitable to Epiphany's partitioned global address space), iii) OpenMP [Ope13] via the OMPi compiler [APD15] (for automatic thread-based parallelization via code pragmas), and iv) MPI [mpi15] using the Threaded MPI implementation [RRPS15] (for distributed parallel computing on the Epiphany grid based on message passing). This flexibility results from the MIMD nature of Epiphany's architecture, that supports many parallel programming models.

#### Hybrid Approaches

Different approaches may also be mixed, in line with an Hybrid Programming approach, often used in Heterogeneous Systems. For instance, at the host-side, the application developed for this work explores conventional POSIX Threads (Pthreads) [But97], either isolated, or combined with OpenMP threads. For co-processor offloading, both the lowlevel eSDK eLib and the OMPi compiler were selected. These approaches give rise to several implementation combinations, later fully described and evaluated in this work.

#### 2.3.3 Use Cases

Due to its specificities, like its memory architecture (see section 2.3.1), the Parallella board often requires a low-level approach to application development. There are, however, many examples that were able to explore its potential. For instance, Gener et al. [GYG15] compared the Parallella with a GPU for spatial domain video filtering, showing that in such scenario the Parallella offers an efficient low-cost and low-power alternative. Taking advantage of the Epiphany co-processor, by using a combination of task and data parallelization, and fine-grained data pipelining, Brauer et al. [BLM16] were able to decrease the processing latency of a typical signal processing chain in more than 50%. Vaas et al. [VRH<sup>+</sup>16] investigated if smart control units used for frequency conversion could benefit from highly parallel hardware accelerators, namely the Epiphany co-processor, and achieved speedups of 1.78 with a limited increase (9%) on power consumption.

### 2.4 The Raspberry Pi family of SBCs

Raspberry Pi is a very popular line of single-board computers, with all the core hardware components (CPU, RAM, GPU and IO controllers) integrated into a single small card, and supporting connection of several external devices (monitor, mouse and keyboard, and others through a General Purpose Input Output (GPIO) connector). These SBCs were created with the goal of promoting a simple and easy platform to learn programming and become familiar with computer technology [Joh12]. However, an increasing number of companies are taking advantage of Raspberry Pi technology and uses these boards as part of their end products.

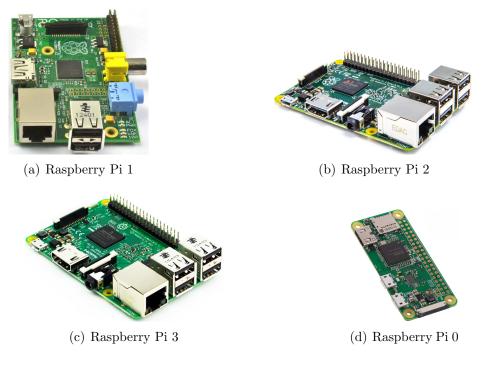

The first version (Raspberry Pi 1) was available to the public in 2013, having a 700 MHz single core ARM CPU and 512MB of RAM. In February 2015, the Raspberry Pi 2 was launched, with a quad-core 900 MHz ARM CPU and 1 GByte of RAM. This was followed by the Raspberry Pi Zero in November 2015, with a 1 GHz single-core ARM CPU and 512 MB of RAM, the goal being to promote a very cheap computer. The last significant evolution on the Raspberry Pi line is represented by the Raspberry Pi 3, launched in February 2016, with a quad-core 1.2 GHz ARM CPU and still 1 GByte of RAM. These four models, illustrated in Figure 2.2, are in fact the ones used in this work.

Raspberry Pi can run many free and open-source Linux or FreeBSD-based operating systems. The most popular is Raspbian, a Debian-based Linux operating system, with

Figure 2.2: Main Raspberry Pi models

over 35,000 pre-compiled packages available [Fou17b]. Raspbian was used in this work, with the same configuration across all four Raspberry Pi boards.

There are many case studies that cover object tracking assisted by Raspberry Pi SBCs, like [MPG15, SS16], to cite just a few. This, and the popularity of these SBCs, make them an obvious choice for comparison with alternative platforms, like the Parallella board.

### 2.5 RGB-D Sensor

RGB-D sensors were introduced in 2010 by Microsoft's Kinect device, a peripheral originally developed for the XBOX 360 gaming console, but that may also be connected to a computer using a simple USB adapter and an external power supply. The RGB-D sensors include an RGB sensor that is able to capture frames with three colour channels (Red, Green and Blue), and a depth sensor that can get an image frame that represents objects distance to the camera. Besides the RGB and depth sensors, Kinect also has a microphone array. In 2013 a second version of the Kinect device was launched, along with the new XBOX One console. However, this work still explores the original version, once it is enough to accomplish the work goals. The Kinect device used is shown in Figure 2.3, and its main specifications are provided in Table 2.3.

Figure 2.3: Microsoft Kinect

| Frames per second        | 30                                                   |

|--------------------------|------------------------------------------------------|

| Available IR distance    | 0.5m - 4.5m                                          |

| Image size               | 640 x 480                                            |

| Dimensions               | $24.9 \text{cm} \ge 6.6 \text{cm} \ge 6.7 \text{cm}$ |

| Weight                   | 1.4kg                                                |

| Horizontal viewing field | $57^{\circ}$                                         |

| Vertical viewing field   | 43°                                                  |

Table 2.3: Microsoft Kinect specifications (version 1).

#### 2.5.1 libfreenect

libfreenect is an open source library that enables the Kinect device to be used with Windows, Linux, and Mac systems. This library is available for C, C++, Java, and Python languages. It is maintained by the OpenKinect community, that consists of over 2000 members. In this work, libfreenect was used with its C/C++ bindings.

For the C language, libfreenect provide a "synchronous" interface where the program executes the function int freenect\_process\_events (freenect\_context \*ctx) by which it blocks and returns data through callback functions previously configured. This behaviour can be implemented by using a thread to handle the callbacks and a buffer to provide an interface for the client.

libfreenect for C++ implements a thread, created in the device class constructor, and that dies when the object is destroyed. The programmer needs to define the callbacks methods in its device class implementation. It should be pointed out that in the C++ class is impossible to control the image buffers; thus, one needs to implement a special separate buffer and to copy the image there during the execution of the callback function. On the other hand, with libfreenect for C, is possible to directly set, access and manipulate the image buffers, facilitating further processing and improving performance.

### 2.6 Profiling Tools

#### 2.6.1 Valgrind

Valgrind is a free and open-source software that helps to detect errors in programs due to incorrect dynamic use of memory, such as memory leaks, incorrect allocation and deallocation, and access to invalid areas. It uses a virtual machine to simulate the memory access of the program under test, eliminating the need to use other auxiliary libraries or drastic code changes. Made for C or C++ coded programs, the virtual machine makes possible to use Valgrind with programs that have been encoded in other languages, such as Java. By using other tools that come with Valgrind, it is possible to optimize the use of the processor cache, locate regions of memory accessed concurrently, and obtain memory usage statistics, as well as measure the execution time of parts of a program [Val17b].

The code of the programs that are being executed by Valgrind do not execute directly on the processor of the machine, being before translated to another intermediate representation, named *ucode*, where that code is executed. This justifies the great loss of performance when running programs with Valgrind, while allowing full monitoring of the running program of libraries without connecting additional libraries.

Throughout the development of this work, Valgrind was regularly used in order to validate the robustness of the code developed, detecting possible bad memory management and threading bugs. Initially, Valgrind was also used to measure execution times, using the Callgrind tool. Callgrind is a built-in Valgrind tool, capable of measuring the execution time and generating function call history (and call graphs) with information about an application's runtime [Val17a]. To run the application through callgrind one executes the valgrind --tool=callgrind prog> command, where prog> is the application. The result of this is a call graph file, with information about the functions that spend more time during the execution. This call graph can be visualized using the KCachegrind program [Wei17]. In this work, callgrind was only used in the initial development stages, and was quickly abandoned in favour of gprof, once this tool has a much less noticeable overhead when used in the Parallella environment.

#### 2.6.2 Gprof

Gprof is a tool of the GNU Binutils binary tool-kit [Fou14] that allows the analysis of binary programs by collecting informations on the most requested functions, including number of calls, and execution time (absolute and relative) [IBM17].

To collect runtime data, Gprof needs the executables to have been generated with profiling support; when using the GNU C++/C compilers, this is ensured by the -pg compilation option; this option will instruct the compiler to add debugging flags and some extra code in the executable that produces the profiling information. After the execution of the program (if it does not end with errors), it is generated the file named gmon.out with information about the execution; this file is interpreted by the Gprof tool to generate a text file with a table that contains the profiling data in an friendly format, and also data that may be used to generate a call graph.

### 2.7 Robot Operating System

The Robot Operating System (ROS) is a framework designed to make it easier to write robotics software. It is a set of tools, libraries, and conventions that simplify the creation of complex and distributed robot systems. It was created because software development for robots is "hard" and from the robot's perspective, problems that seem trivial to humans often vary wildly between instances of tasks and environments [Fou17a].

This work has put considerable effort trying to port to and run ROS in the Parallella Linux environment, with the aim of simplifying and automating, as much as possible, the capture, pre-processing and pos-processing of frames from the Kinect sensor. Unfortunately, such effort was not 100% effective, the conclusion being that there seems to exist a fundamental incompatibility between the Parallella runtime environment and ROS (most probably at the USB subsystem). This failure lead the work towards a lower-level custom approach, directly exploring libfreenect facilities.

### Chapter 3

## General Structure and Initial Version

This chapter presents the general structure of the object tracking application developed in this work, along with a first functional version and results of some preliminary tests. This made possible the identification of some bottlenecks, and opportunities for improvements that are necessary for execution under the constraints of the Parallella platform.

### 3.1 Main Components and Stages

Figure 3.1: General Structure of the Tracking Application.

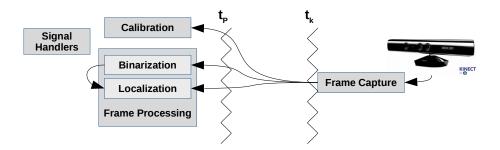

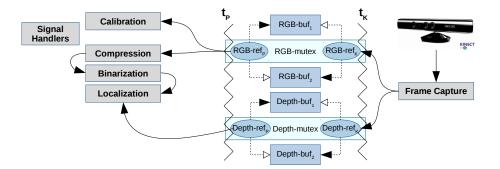

The general structure of the tracking application developed in this work is represented in Figure 3.1. It includes several components, namely: i) Frame Capture, that captures frames from the Kinect sensor; ii) Calibration, active only at the beginning of execution; iii) Frame Processing, that makes each frame go through several transformations and processing stages (Binarization and Localization) in order to achieve object tracking (it also allows for the visualization of frames in all processing stages using OpenCV); iv) Signal Handlers, used to control application execution and to trigger feedback from it.

#### 3.1.1 Concurrent Processing with Pthreads

The application components are bound to two threads:  $t_K$ , that loops through the Frame Capture code;  $t_P$ , that performs the initial Calibration and then loops through the various stages of Frame Processing. The main reason to split the application in two distinct threads is to avoid overloading frame capture with further frame processing, which could delay capture of subsequent frames and generate frame loss; thus, by relieving the frame capture thread from frame processing tasks, the capture of frames may be performed at the maximum rate supported by the Kinect sensor; this was confirmed by preliminary tests with the Parallella board: the frame rate of a single thread, running at the hostside, and performing frame processing in addition to frame capture would be under 30fps; thus, the use of more than one thread becomes imperative if no frame loss is admissible.

The  $t_K$  and  $t_P$  threads are based on the POSIX Threads (PThreads) standard [But97], for portability and performance reasons. In addition to the use of the PThreads model as the basic foundation for the developed application, other processing strategies were also intermixed (namely in the different stages of the frame processing), to improve performance. The hybrid approaches pursued in this work are addressed in the next chapter.

#### 3.1.2 Frame Capture

The  $t_K$  thread captures frames from the Kinect sensor using libfreenect [Ope17c] facilities. This is achieved using two callback functions: one for RGB frames, another for Depth frames. These callback functions work with a pair of MUTEX locks and a condition variable to control access to the shared data structures where  $t_K$  writes Kinect frames and from where  $t_P$  collects them for further processing. Figure 3.2 provides a simplified representation of this frame transfer mechanism.

When a new frame is received from Kinect, the  $t_K$  thread tries to lock a specific mutex

Figure 3.2: Frame transfer from  $t_K$  to  $t_P$  (general view).

(RGB-mutex, or Depth-mutex) using a non-blocking locking. If the locking succeeds,  $t_K$  performs the operation that provides the frame for  $t_P$  (a full copy of the frame in the initial version of the application, or a simple pointer switch coupled with a pair of buffers in the final version) and signalizes  $t_P$  that a new frame is available; otherwise, if locking fails, it means that the  $t_P$  thread has previously acquired the lock and is still accessing the critical memory region; in this case, the  $t_K$  thread proceeds to capture a new frame discarding the current frame.

The  $t_P$  thread performs a blocking lock to get an available frame. After succeeding, checks if the available frame is new; if it is a new frame it continues to do its processing; otherwise,  $t_P$  sleeps waiting to be notified from  $t_K$  thread that a new frame is available.

#### 3.1.3 Calibration

The purpose of Calibration is to capture the RGB colours of the object to be tracked in the RGB frames. This is done once, by the  $t_P$  thread. The calibration uses a OpenCVmanaged window, as shown in Figure 3.3, where the purple rectangle (drawn by the user) delimits the area containing the relevant colours; all the colours obtained are stored in a structure to be used in the Binarization stage.

A common characteristic shared by the various approaches tested for RGB Calibration was to ignore some least significant bits of each byte of an original object RGB pixel. The reason behind this is twofold: i) captured RGB frames usually show some colour noise to the extent that close colours may be considered equal; ii) having to store fewer bits per channel may translate in storage savings (which may be relevant in memory constrained

Figure 3.3: Initial RGB Calibration.

scenarios) and even faster searches (once there are less possible colour variants).

#### 3.1.4 Frame Processing

As Figure 3.1 shows,  $t_P$  processes frames through two main different stages: i) (RGB) Binarization, and ii) (RGB+Depth) Localization. These stages are discussed next.

#### **RGB** Frame Binarization

The goal of this stage is to produce a new version of the original RGB frame, with only two colours: white for pixels belonging to the object tracked, and black for the remaining pixels – see Figure 3.4. Without any compression of the original frame, the size of this "binary" version of the frame will be 1/3 of the size of the original frame, once each pixel will be represented by a single byte with 255 (white) or 0 (black) values.

This is achieved by following a simple procedure: for each pixel of the original RGB frame, it is performed a search on the calibration structure, to check if the pixel colour is one of the detected colours during the calibration stage.

Figure 3.4: Binarization Process (before and after).

#### **Object Localization**

This stage takes the  $\langle X, Y \rangle$  coordinates of all object pixels (white pixels) in the binary RGB frame (produced in the previous stage), and computes their average. The outcome of this stage is a single pair of coordinates,  $\langle X', Y' \rangle$ . These coordinates are then used to recover a Z' coordinate in the Depth frame as follows: to minimize the noise influence, it is calculated the average Z' of all Depth values of a tile of  $3 \times 3$  centered on the  $\langle X', Y' \rangle$  position in the Depth frame. This completes the localization of the object in the frame.

Figure 3.5 shows the result of the location stage of the object, where the target is over the object tracked in the image, and its final  $\langle X', Y', Z' \rangle$  position (in the context of the frame coordinates) is shown.

Figure 3.5: Representation of Object Position.

### 3.1.5 Signal Handlers

The Signal Handlers component includes routines to be executed by the thread  $t_P$  upon the arrival of certain POSIX signals (software generated interrupts). The generation of those signals is currently achieved through the kill shell command. The signals are sent to the application to trigger certain actions, as described in Table 3.1.

| Signal Name | Signal Number | Action                                             |  |

|-------------|---------------|----------------------------------------------------|--|

| SIGINT      | 2             | Stop the Application (Clean Exit).                 |  |

| SIGALRM     | 14            | Execute Signal 10 handler, and reprogram the       |  |

|             |               | next Signal 14 arrival.                            |  |

| SIGUSR1     | 10            | Show the current state of the program.             |  |

| SIGUSR1     | 30            | Show the last image incoming from Kinect (with     |  |

|             |               | a target over the object), and its binary version. |  |

| SIGUSR1     | 16            | Start Calibration.                                 |  |

Table 3.1: POSIX Signals captured by the application and actions triggered.

As an example, Figure 3.6 shows an application output after receiving a signal 10.

| Number of frames pairs (RGB + Depth) processed                                                                                                                                   | 869      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Number of RGB frames lost<br>Number of Depth frames lost<br>Number of times none RGB frame was available to process<br>Number of times none Depth frame was available to process | 0<br>220 |

| Number of times the object tracked was not found in the scene:                                                                                                                   | 0        |

| Current X Coordinate<br>Current Y Coordinate                                                                                                                                     |          |

| Current Z Coordinate:                                                                                                                                                            | 810      |

Figure 3.6: Output of the Signal 10.

The way in which the application detects and reacts to signals is as follows. Because signals are an asynchronous notification mechanism, it is desirable to execute the smallest possible amount of code, and only certain types of code (like changing the value of an integer variable), in order to avoid breaking the consistency of the application (which may theoretically get interrupted anywhere). Thus, when  $t_P$  receives a signal, only a global flag is changed, from zero to the respective signal number, and the action specified in Table 3.1 is postponed to the beginning of a new iteration of the processing loop. Before going after the next frame, the processing loop in  $t_P$  checks the flag; if the flag tells a signal has been received, it will execute the proper action and after it will reset the flag.

An exception occurs at the beginning of the application execution, where the Calibration needs to be executed before the image processing loop. In this case the flag assumes the value 16. The application verifies this flag and executes the calibration like if it had received a signal, and after it executes the image processing loop.

During signal handling, the  $t_K$  thread is not affected. This thread continues the capture of frames, but these end up getting discarded if  $t_P$  gets delayed.

# 3.2 Initial PThreads Version

This section documents the preliminary efforts towards a functional (prototype-level) object tracker, based on Pthreads. These efforts already include some preliminary evaluation tests that pave the way to several optimizations added in the final Pthreads version.

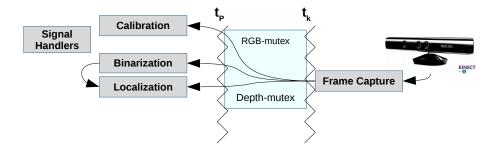

## 3.2.1 Frame Capture

Initially, frame capture was performed using facilities offered by libfreenect for C++. This library provides the Freenect::Device class that needs to implement two callback virtual methods: one for RGB frames (void VideoCallback(void\* \_rgb, uint32\_t timestamp)), and the other for Depth frames (void DepthCallback(void\* \_depth, uint32\_t timestamp)). These callbacks methods are invoked when a new RGB/Depth frame is made available by the Kinect sensor, receiving a reference (pointer) to the frame as input parameter. Before returning, the callbacks copy (by value) the frames to separate buffers. These are the RGB-buf and Depth-buf buffers represented in Figure 3.7.

In turn, the processing thread,  $t_P$ , will also copy the content of intermediate buffers RGB-buf and Depth-buf to its own buffers. The consistency of these operations is ensured by the mutual exclusion mechanisms put in place, already presented in section 3.1.2.

Figure 3.7: Frame transfer from  $t_K$  to  $t_P$  (initial version: by copy)

## 3.2.2 Calibration

Calibration implementation started by exploring two different data structures, with the goal of finding a way to store calibration data with minimal memory space and still good access performance. These preliminary calibration data structures are discussed next.

#### Dynamic RGB Vector

In this approach the specific RGB colours of the tracked object are inserted, one-by-one, into a dynamically allocated vector, based on the std::vector<colorID> type, where colorID is a 32 bit unsigned integer. Colours are sorted by the colorID 32 bit value and the class used provides access to a specific colorID using internally a binary search.

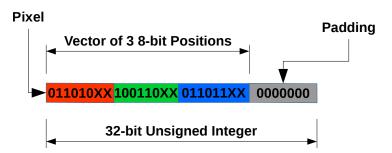

The internal structure of the colorID data type is shown in Figure 3.8. It includes 1 byte per each RGB channel, and a 1 byte padding. The padding ensures the colorID type consumes 32 bits, thus being memory aligned, which improves access speed; moreover, it makes searching for colours easier (once it is enough to compare full 32 bit integers), and faster (because the CPU can use only one instruction to make comparisons).

In line with what was stated in section 3.1.3, only 6 bits per RGB channel are considered; the others are ignored (zeroed, in fact); this is conveyed, in Figure 3.8 by the special symbol 'X'. However, in this approach those ignored bits still consume storage space.

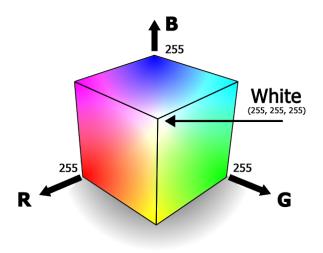

#### Static RGB Cube

This variant uses a 3-dimensional static array, also known as RGB cube in this context. (a geometric representation of the RGB cube is shown in Figure 3.9). The presence/absence

Figure 3.8: Internal structure of the colorID data type.

of a specific RGB colour in the object is represented as a True (1) / False (0) boolean value in the specific RGB cube cell of that colour.

Figure 3.9: RGB colour space

Considering 8 bits per each RGB channel, the RGB cube would have  $2^8 \times 2^8 \times 2^8 = 2^{24} = 16M$  elements of 1 boolean byte each, thus consuming 16 MBytes of storage. However, each channel byte of an RGB pixel of the tracked object is still stripped of the least 2 significant bits when defining the RGB cube coordinates that will have the value True. This means that the RGB cube can be much smaller, with only  $2^6 \times 2^6 \times 2^6 = 2^{18} = 256K$  elements, thus consuming only 256 KBytes. Nevertheless, the Static RGB Cube still consumes much storage space than the Dynamic RGB Vector. The big advantage of the Static RGB Cube approach is that it supports direct access to the intended element,

which is faster than the binary search used in the Dynamic RGB Vector approach.

#### 3.2.3 RGB Frame Binarization

The Binarization stage relies on access to the data structures produced during Calibration to perform the binarization of the RGB frames incoming from Kinect. Thus, with two different Calibration data structures, there are at least two different approaches to Binarization: with the Dynamic RGB Vector, or with the Static RGB Cube.

Those data structures may, however, benefit from extra information gathered during Calibration, that may be used to accelerate the Binarization process. This extra information consists on the lowest and highest Red, Blue and Green values observed for the tracked object. The idea is then to immediately discard, as not belonging to the tracked object, a frame RGB pixel if at least one of its Red, Blue and Green values are out of the ranges observed during Calibration; otherwise, the Calibration data structures will still have to be searched, to confirm if the RGB pixel belongs to the object; this confirmation is necessary because it is not enough for the Red, Green and Blue values to fall in the expected ranges: typically, only some of the combinations of those in-range values are valid. The Binarization variants that take advantage of this simple segmentation method carry the suffix "with Threshold" on their name.

A sum up of the four initial approaches to RGB Frame Binarization is presented next.

#### **Dynamic RGB-vector**

To check if the RGB colour of a RGB frame pixel belongs to the tracked object, convert that RGB colour to the ColorID format and trigger a search for it in the Dynamic RGBvector, taking advantage of the binary search provided by the C++ STL [Int17].

#### Dynamic RGB-vector with Threshold

Like the previous approach, but preceded by an extra test: only conduct the search in the Dynamic RGB-vector if the Red, Green and Blue values of the RGB pixel are all within

the valid ranges, for each channel, identified during Calibration.

#### Static RGB-cube

To check if the RGB colour of a RGB frame pixel belongs to the tracked object, convert each RGB channel from 8 bits to 6 bits and then use the three 6 bits values as coordinates for direct access to the Static RGB-cube.

#### Static RGB-cube with Threshold

Like the previous approach, but preceded by an extra test: only conduct the search in the Dynamic RGB-vector if the Red, Green and Blue values of the RGB pixel are all within the valid ranges, for each channel, identified during Calibration.

This technique virtually searches a "sub-cube or sub-parallelepiped" inside the RGBcube, that encompass all colours within the ranges identified during Calibration.

## 3.2.4 Preliminary Evaluation

This section presents the results of an evaluation of the initial application version.

The evaluation was conducted on a Parallella-16 Desktop Computer board, taking advantage only of its dual core ARM CPU, once the initial application version was only based on Pthreads and thus not yet capable of exploring the Epiphany co-processor.

In all tests the Kinect sensor was pointed to the same scenario, and the object tracked was the same as well as the luminosity conditions (once the object was static). In order to ensure fairness in the evaluation of the four variants, the number of colours picked during Calibration was always the same<sup>1</sup>: 2048 RGB colours; this number was chosen having in mind memory constraints for a future Epiphany version (the space necessary to store a vector of 2048 RGB colours – with 4 bytes per colour, due to memory alignment requisites – would be 8 KBytes, that is, the capacity of an eCore local memory bank).

<sup>&</sup>lt;sup>1</sup>Sometimes requiring the capture of more than one frame during Calibration.

The executables were generated with GNU compilers (g++ for C++ code, and gcc for C code), using the -Os option (enables all -O2 optimizations that do not increase code size, which is adequate for embedded systems, that typically have limited memory). Execution times were measured using gprof [FSB98].

#### Frame Capture Time

Initially, the application was fully based on C++, and only g++ was used to generate the executable(s); however, the frame capture times of this version were measured to be very high, being around 63ms, well above the time necessary (33 ms) to ensure a frame capture rate of 30 fps; the culprit was then found to be the time spent by the RGB and Depth callbacks to copy the frames to the intermediate buffers shared with the processing thread (RGB-buf and Depth-buf in Figure 3.7). After some unsuccessful attempts to solve the problem, the drastic option was taken to rewrite the frame capture module exclusively in C, and compile it with gcc. The net result was the decrease of the frame capture time from  $\approx 63$  ms to  $\approx 43$  ms. Despite the improvement, this late value is still above the desired time (33 ms), and extra optimization efforts were necessary (see next chapter).

#### Frame Processing Time

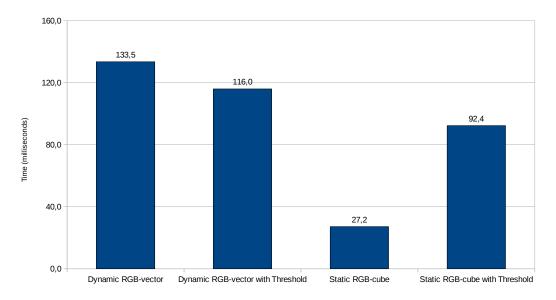

To evaluate the frame processing time, four variants of the initial application were tested, each using one of the four approaches (presented in section 3.2.3) for the RGB Frame Binarization stage. The results, measured in milliseconds, are shown in Figure 3.10, as averages, considering 5 runs of each executable and a limited sample of 2000 frame pairs (RGB+Depth) per run. The results also include the time spent by the the  $t_P$  thread to copy data from the intermediate buffers shared with the capture thread (RGB-buf and Depth-buf in Figure 3.7), to its own buffers; together, these times are less than 10 ms, and so the bulk of the time is really spent in the Binarization and Localization stages.

The results clearly show that using a Dynamic RGB-vector, even with the Threshold optimization, is always outperformed by the Static RGB-cube approach.

The underwhelming performance of the Dynamic RGB-vector approaches is due to the

Figure 3.10: Frame processing time in the initial version (ms).

time spent in binary searches: with 2048 RGB colours and no Threshold optimization, the maximum number of comparisons is 11, and this is the effective number of comparisons most of the time, because the object tracked is typically small in comparison to the scene; on the other hand, with the Threshold optimization, there will always be 6 initial comparisons, that eliminate the vast majority of candidates (and so only a small number will pass the test, and imply a binary search); however, the impact of those 6 comparisons is still very high, to the extent that the Dynamic RGB-vector with Threshold approach has a speed-up of only 133,5/116 = 0,1509 over the Dynamic RGB-vector approach.

The cost of the 6 initial comparisons is also very high in the Static RGB-cube with Threshold approach, such that it pays off to always access the RGB cube, as done by the Static RGB-cube approach. The speed-up relative to the Static RGB-cube with Threshold approach is, in this case, 92,4/27,2=3,3971. As such, the Static RGB-cube approach was chosen as the base approach for the final application version, with adaptations necessary to cope with the memory constraints of the Epiphany co-processor (see next chapter).

Finally, it should be said that the average frame processing time of 27,2 ms ensured by the Static RGB-Cube approach is already below the limit of 33,(3) ms for a single frame, as imposed by the Kinect nominal sampling rate of 30 fps. As threads  $t_P$  and  $t_K$  are able to run simultaneously (if at least two cores are available), this means that, as soon a  $t_K$  has captured a frame,  $t_P$  will immediately grab it and will become ready to grab the next frame slightly before it arrives. It also means that there's a delay of  $\approx$ 27,2 ms from the moment that a frame is made available (by  $t_K$ ) to the moment that its processing ends (and its possible effects manifest) or, equivalently, "processing is always one frame behind". Shrinking this gap makes the application to follow more closely what happening in the real scene, and may even free enough time for other features, like visualization. In the next chapter, several optimizations are explored, including parallel processing techniques, in order to achieve even lower frame processing times.

# Chapter 4

# **Optimized and Hybrid Versions**

This chapter starts by presenting a set of optimizations that decrease the storage requisites and enhance the performance of the PThreads version of the objet tracking application, as shown by a second round of tests. It then introduces the parallel programming models used to try to further improve the performance of PThreads version: OpenMP and the Epihany eSDK. For each hybrid approach, performance results are presented. The chapter ends with a final discussion on the performance achieved by the different approaches used. A comparison is also provided with several models of the Raspberry Pi platform.

# 4.1 Optimized PThreads Version

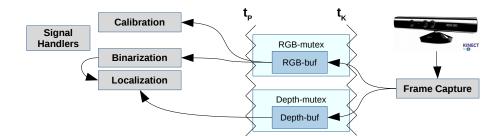

As shown in section 3.2.4, the way in which frames are transferred, from the  $t_K$  thread to the  $t_P$  thread, in the initial version of the application, imposes a significant performance penalty, even preventing frame capture to be conducted at the Kinect sensor nominal rate (33 fps). On the other hand, the size of several important data structures, namely the captured frames and the RGB-cube produced/used during Calibration and Binarization, are still inadequate to the memory constraints of the Epiphany grid of eCores.

The problems above identified are solved in the final iteration of the tracking application. The general structure of that optimized version is presented in Figure 4.1: it is based on a new strategy for the transfer of frames between  $t_K$  and  $t_P$ , and there's also a

Figure 4.1: General Structure of the Optimized Version.

new Compression processing stage. These enhancements are discussed along this section.

#### 4.1.1 Frame Capture

The change of the code base of the frame capture module from C++ to C allowed not only to decrease the frame transfer times (although still not enough), but also opened the opportunity to explore the facilities of libfreenect for C in order to directly control the pointers that Kinect uses to reference the buffers where captured frames are deposited.

The new approach still uses separate callback functions for RGB frames and Depth frames. Each callback uses a pair of buffers (<RGB-buf<sub>1</sub>, RGB-buf<sub>2</sub>>, and <Depth-buf<sub>1</sub>, Depth-buf<sub>2</sub>>) and each pair of buffers is referenced by a pair of global pointers (<RGB-ref<sub>*R*</sub>, RGB-ref<sub>*K*</sub>>, and <Depth-ref<sub>*P*</sub>, Depth-ref<sub>*K*</sub>>), visible in both  $t_K$  and  $t_P$ . Pointers RGB-ref<sub>*K*</sub> and Depth-ref<sub>*K*</sub> reference the buffers that  $t_K$  will use to receive the next RGB and Depth frames. Pointers RGB-ref<sub>*P*</sub> and Depth-ref<sub>*P*</sub> reference the buffers that hold the previous RGB and Depth frames to be processed by  $t_P$ . The pointers switch the buffers that would delay the processing of the current frame and the capture of the next. The same pair of locks (RGB-mutex and Depth-mutex) are still used, to protect access to the pointers (and their pointed buffers), following the same logic described in section 3.1.2.

#### 4.1.2 Calibration

The preliminary evaluation discussed in section 3.2.4 showed the Static RGB-cube approach to be the most performant. On the other hand, even with only 6 bits per RGB channel, the RGB-cube still consumes 256 KBytes, making it impossible to fit one copy in the limited 32 KBytes local memory of each eCore (other options, like placing the RGB-cube in shared memory, or even to scatter it among the 16 eCores, would entail worse performance, specially the last alternative). Therefore, extra compression is needed.

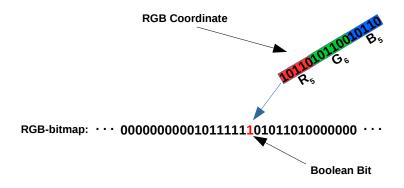

First, the size of Red and Blue coordinates is further reduced one bit, so that, in the end, the Red, Green and Blue bytes loose the least significant 3, 2 and 3 bits, respectively; this transformation can be represented by  $\langle R_8, G_8, B_8 \rangle \rightarrow \langle R_5, G_6, B_5 \rangle$  (this finds ground on the fact that captured RGB frames usually show some color noise, to the extent that close colors may be considered equal and through preliminary testing, it has been observed that there is better performance if the green color has a higher resolution compared to other possible combinations of color resolution). This reduces the overall number of  $\langle R, G, B \rangle$  coordinates to  $2^5 \times 2^6 \times 2^5 = 2^{16}$ , producing a new RGB calibration data structure, that takes only 64 KBytes (still using 1 boolean byte per RGB colour). This new data structure is 1-dimensional, indexed by a  $R_5G_6B_5$  2-byte coordinate.

Further compression is achieved by replacing each boolean byte by a boolean bit, in the RGB calibration data structure, as it shows Figure 4.2. This final structure, hereafter named **RGB-bitmap**, thus becomes a 1-dimensional vector, with 64 Kbits, now taking only 8 KBytes, thus perfectly fitting in one of the four local memory banks of each eCore.

#### 4.1.3 **RGB** Frame Compression

This new stage reduces the RGB frame size. It aims to allow the RGB image (not the original, but a compressed version) to fit into each eCore's local memory (1/16th of the image, per eCore). Besides reducing frame size, compression also reduces color noise and increases the processing speed of further stages (as they have less RGB pixels to process).

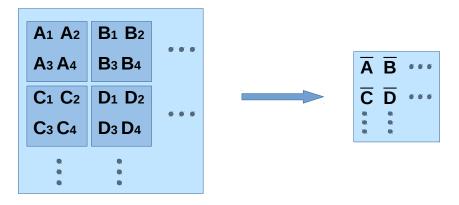

RGB frame compression is achieved as follows: the original  $640 \times 480$  RGB frame is

Figure 4.2: RGB-bitmap calibration data structure.

downscaled to  $320 \times 240$  (each dimension is halved), by averaging tiles of  $2 \times 2$  adjacent pixels, producing a smaller frame with 1/4th of the size of the original (900  $\rightarrow 225$  KBytes) as shown in Figure 4.3.

Figure 4.3: First phase of the RGB Frame Compression: Pixel Averaging.

A second phase of compression is then performed over the outcome of the first phase: the RGB colour of each RGB pixel is downsized from 24 bits to 16 bits, using the same technique applied to the RGB coordinates of the RGB-bitmap (see above). This further reduces the frame size in  $2/3^1$ , going down from 225 KBytes to 150 KBytes (9,375 KBytes per Epiphany core). Furthermore, the  $R_5G_6B_5$  pixels in the final reduced frame can now be used as RGB coordinates for direct access to the RGB calibration bitmap. The Figure 4.4 shows the outcome of the two phases of the compression.

Although presented here separately, the two phases of the RGB Frame Compression

<sup>&</sup>lt;sup>1</sup>For a total reduction of  $1/4 \times 2/3 = 1/6$  with relation to the original size of 900 KBytes.

Figure 4.4: Frame Compression Process (before and after).

stage are performed together, for each pixel, in a single loop, for performance reasons.

## 4.1.4 RGB Frame Binarization

The Binarization stage now needs to take into account the new RGB-bitmap as the optimized Calibration data structure: it goes through each  $R_5G_6B_5$  16 bit colour of each pixel of the RGB frame compressed, and uses that 16 bit value as a 1-dimensional coordinate in the RGB-bitmap, to get the corresponding boolean bit. Because the RGB-bitmap is primarily byte-addressed, it is first necessary to compute the index of the byte that holds the intended bit (see Equation 4.1); then, the value (0 or 1) of the intended bit may be easily extracted from the referenced byte (see Equation 4.2).

$$byteIndex = RGBcolor/8 \tag{4.1}$$

$$bitValue = (128 >> (RGBcolor\%8)) \& RGBbitmap[byteIndex]$$

(4.2)

The size of the binary frame will be 1/2 of the RGB compressed frame, thus taking 150 KBytes / 2 = 75 KBytes, or 1/12 of the original uncompressed RGB frame.

#### **Object Localization**

This stage follows the description provided in section 3.1.4, with an additional adjustment: the coordinates  $\langle X',Y' \rangle$  are doubled before recovering the Z' coordinate in the Depth frame, at position  $\langle 2X',2Y' \rangle$  ( $\langle X',Y' \rangle$  refers to a 320 × 240 binary frame, but the Depth frame was not compressed and thus preserves its original 640 × 480 resolution).

#### 4.1.5 **Preliminary Evaluation**

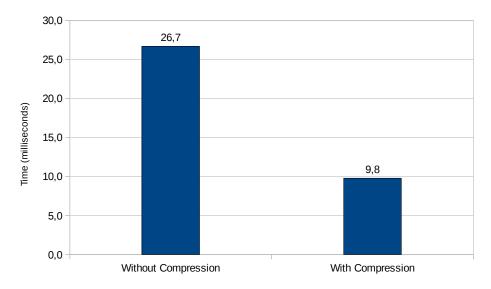

To measure with more accuracy the frame processing time, it was decided to replace the usage of gprof by instrumenting the code with calls to the POSIX function gettimeofday. The processing times presented are still averages of 2000 samples per run, and each test is still executed in 5 runs. This methodology was adopted for the remaining of the work.

The frame processing times of the initial and optimized Pthreads version, measured under the new methodology, are shown in Figure 4.5.

Figure 4.5: Frame processing time (ms): initial vs optimized Pthreads version.

The new evaluation methodology is clearly less intrusive, once the time measured for the initial version is now 26,7 ms, slightly below the 27,2 ms previously measured (see Figure 3.10). Regarding the optimized version, the two optimizations applied (a new frame transfer strategy between  $t_K$  and  $t_P$ , and the use of Compression on the captured frame and the Calibration data structure), were able to provide a respectable speed-up of 26,7/9,8=2,7. And, as important as this performance improvement, the main data structures have now adequate sizes to be stored in the local memory of the Epiphany eCores, thus making possible to finally explore the Epiphany co-processor.

Trying to further improve the performance of the optimized Pthreads version, three hybrid approaches were developed that build on this version: the first explores OpenMP; the second explores the low-level Epiphany Software Development Kit (eSDK); the final one mixes OpenMP and the eSDK. These approaches are described in the next sections.

# 4.2 Parallel Processing with OpenMP

OpenMP was explored as a straightforward way for automatic (many-)thread parallelization of all frame processing stages. These stages are particularly suitable to parallelization due to independent accesses and processing of the data structures involved.

In the Parallella board, OpenMP may be used to take advantage either of the dualcore ARM CPU or of the Epiphany many core co-processor. This implies the use of two different OpenMP implementations: the ARM CPU was targeted by the native OpenMP facilities of the C/C++ compilers used; the Epiphany 16-core co-processor required the use of OMPi, a separate OpenMP implementation. These two ways used to explore OpenMP are explained next.

### 4.2.1 Host-only OpenMP

The OpenMP version that targets the ARM CPU was used for automatic parallelization of for loops in the Compression, Binarization and Localization (RGB only) stages, by prepending each loop with proper "pragma" directives. For the Compression and Binarization stages, the directive was **#pragma omp parallel for**, in a single loop in each stage. To compute the average coordinates  $(\overline{X}, \overline{Y})$  in the RGB Localization, a more specific directive (reduction) was used to sum automatically the results of every thread in a single variable for each result: **#pragma omp parallel for reduction(+:sumX,sumY,numElems)**. These directives allow to separate data and work automatically among the processing cores available in the platform. The number of threads the application uses is set up by an ambient variable (by default, its value is the number of processing cores available).

It is possible to change the way that these directives work, as controlling the amount of data that each OpenMP thread will process, or turn the operation of separating the data from dynamic (default) to static. Several tests showed that the default way to use the directives is the most effective way.

## 4.2.2 Epiphany-specific OpenMP

When using OMPi, it is possible to compile only C 99 code; however, the frame processing thread was based on C++ 11. In order to solve this mismatch, the following strategies were applied: i) the frame processing thread code was rewritten in C language; unfortunately, the OMPi compiler seems to have a bug that makes impossible to compile code that uses, at the same time, **pragma** directives and calls to the C-based OpenCV library; ii) to solve the previous problem, the code with **pragma** directives was moved to a different file and compiled separately; however, the OMPi compiler was unable to link that file with files having calls to the C-based OpenCV library; iii) as a last attempt, code with pragmas was kept in C and was compiled with the OMPi complier, and for the remaining code its C++ version was used again and compiled with g++; the linkage of the object files was made with OMPi; this convoluted strategy solved the compilation problem and produced an executable that runs without crashes.

Another problem found was that vectorization was not fully implemented by the OMPi compiler. In its current development state, OMPi can only send a statically allocated vector (as if it were a simple scalar datum) to the Epiphany co-processor (providing a pointer to a vector, along with its size, does not work). Thus, to send the compressed RGB frame and the RGB-bitmap to the co-processor, it was necessary to declare global static instances for those data structures, in the application module having the pragma directives. In the C++ application module, extern directives allow to access those static

structures through pointers.

Only the Binarization and RGB Localization stages were parallelized, using pragma directives for loop parallelization, similar to those used with ARM CPUs. However, these directives were preceded by three additional OMPi specific directives: i) pragma omp target data map(to:staticRGBframe,staticRGBbitmap) map(from:sumX,sumY,num PixelsObj), ii) pragma omp parallel private(staticRGBbitmap), iii) pragma omp target. The first two directives ensure the transfer of a copy of the RGB calibration bitmap and 1/16th of the compressed RGB frame to the local (private) memory of the Epiphany cores, and the recovery of the outcome of the RGB Localization. The third directive ensures that subsequent parallel loops execute on the Epiphany device.