## UNIVERSIDADE TECNOLOGICA FEDERAL DO PARANÁ DEPARTAMENTO ACADÊMICO DE ELETROTÉCNICA ENGENHARIA INDUSTRIAL ELÉTRICA - ELETROTÉCNICA

LUÍS FERNANDO GUIMARÃES LUIS GUSTAVO KAWAHARA

# PROJETO E IMPLEMENTAÇÃO DE UMA CARGA ELETRÔNICA

TRABALHO DE CONCLUSÃO DE CURSO

## LUÍS FERNANDO GUIMARÃES LUIS GUSTAVO KAWAHARA

# PROJETO E IMPLEMENTAÇÃO DE UMA CARGA ELETRÔNICA

Trabalho de Conclusão de Curso de Graduação do Curso Engenharia Industrial Elétrica - Ênfase Eletrotécnica do Departamento Acadêmico de Eletrotécnica (DAELT) da Universidade Tecnológica Federal do Paraná (UTFPR) como requisito para obtenção do título de Engenheiro Eletricista.

Orientador: Prof. Roger Gules, Dr. Eng.

#### Luís Fernando Guimarães Luis Gustavo Kawahara

# Projeto e implementação de uma carga eletrônica

Este Trabalho de Conclusão de Curso de Graduação foi julgado e aprovado como requisito parcial para a obtenção do Título de Engenheiro Eletricista, do curso de Engenharia Elétrica – Ênfase em Eletrotécnica do Departamento Acadêmico de Eletrotécnica (DAELT) da Universidade Tecnológica Federal do Paraná (UTFPR).

Curitiba, 10 de abril de 2013. Prof. Emerson Rigoni, Dr. Eng. Coordenador de Curso Engenharia Elétrica – Ênfase em Eletrotécnica Prof. Marcelo Rosa, Dr. Eng. Coordenador dos Trabalhos de Conclusão de Curso de Engenharia Elétrica do DAELT **ORIENTAÇÃO BANCA EXAMINADORA** Prof. Dr. Eng. Roger Gules Prof. Dr. Eng. Roger Gules Universidade Tecnológica Federal do Paraná Universidade Tecnológica Federal do Paraná Orientador Prof. Dr. Eng. Alceu André Badin Universidade Tecnológica Federal do Paraná

A folha de aprovação assinada encontra-se na Coordenação do Curso de Engenharia Elétrica

Prof. Dr. Eng. Eduardo Felix Ribeiro Romaneli Universidade Tecnológica Federal do Paraná À memoria de Aguinaldo Guimarães pelo exemplo e carinho.

#### **AGRADECIMENTOS**

Primeiramente agradecemos aos nossos mestres que tanto nos ensinaram durante todos os anos da nossa graduação, em especial para o nosso orientador, Prof. Dr. Roger Gules. Agradecimentos especiais, também, à nossa banca examinadora, Prof. Dr. Alceu André Badin e Prof. Dr. Eduardo Felix Ribeiro Romaneli, pela atenção que foi dedicada na análise deste trabalho.

À empresa NHS por ter nos auxiliado sempre que necessário. Este trabalho seria impossível sem o auxílio técnico e teórico do Me. Rafael Christiano Annunziato e para ele vai o nosso agradecimento especial. Agradecemos o diretor técnico Eng. Naldir Cardoso por liberar todos os equipamentos que foram necessários para a realização deste trabalho, e por permitir a documentação do mesmo.

Não podemos deixar de agradecer, também, todos os nosso colegas de curso que nos acompanharam nos momentos felizes e difíceis de nossa graduação.

Por fim, mas não menos importante, agradecemos os nossos familiares pelo suporte eterno que nos oferecem até nos momentos mais escuros. Agradecemos também a Deus por nos dar a força necessária para a conclusão deste trabalho e de nossa graduação.

#### RESUMO

KAWAHARA, Luis G.; GUIMARÃES, Luís F. Projeto e implementação de uma carga eletrônica. 2013. 86 f. Trabalho de Conclusão de Curso (Graduação em Engenharia Industrial Elétrica) – Universidade Tecnológica Federal do Paraná. Curitiba, 2013.

Com a alta demanda de energia a sustentabilidade passou a ser uma necessidade. É comum que indústrias utilizem uma grande quantidade de energia em testes de seus produtos e é neste contexto que a importância da carga eletrônica está presente, uma vez que esta é capaz de regenerar grande parte da energia utilizada nesses testes para a rede elétrica. Neste trabalho, é mostrado o projeto e implementação do protótipo da carga eletrônica instalada na empresa NHS de Curitiba, Paraná, em que seu desenvolvimento passou pelas fases de simulação através do software *Simulink*, dimensionamento, projeto dos controles (PI, atraso de fase, repetitivo) e ensaios. Os resultados foram utilizados como base para uma versão final do equipamento.

Palavras chave: carga eletrônica, energia, sustentabilidade, sistemas de controle, PI, atraso de fase, repetitivo.

#### **ABSTRACT**

KAWAHARA, Luis G.; GUIMARÃES, Luís F. Design and implementation of an Electronic Load. 2013. 86 f. Trabalho de Conclusão de Curso (Graduação em Engenharia Industrial Elétrica) – Universidade Tecnológica Federal do Paraná. Curitiba, 2013.

With the high energy demand the sustainability became a necessity. It is common for industries to use a great quantity of energy in product testing and it is in this context that the electronic load is present, since it is able to regenerate most of the energy used to the power grid. This manuscript presents the project and implementation of the electronic load prototype installed at the company NHS from Curitiba, Paraná, where its development was divided in simulation through the software Simulink, design, control project (PI, phase-lag, repetitive) and experiments. The results was used as basis for the final version of the equipment.

Keywords: electronic load, energy, sustainability, control systems, PI, phase-lag, repetitive.

## **LISTA DE FIGURAS**

| Figura 1 – Diagrama de blocos da carga eletrônica                                |

|----------------------------------------------------------------------------------|

| Figura 2 – Carga eletrônica com topologia back-to-back isolada da rede18         |

| Figura 3 - Conversor CC-CA em ponte completa24                                   |

| Figura 4 - Etapa 1 do semiciclo positivo do conversor ponte-completa25           |

| Figura 5 - Etapa 2 do semiciclo positivo do conversor ponte-completa25           |

| Figura 6 - Etapa 3 do semiciclo positivo do conversor ponte-completa26           |

| Figura 7 - Etapa 4 do semiciclo positivo do conversor ponte-completa27           |

| Figura 8 - Etapa 1 do semiciclo negativo do conversor ponte-completa27           |

| Figura 9 - Etapa 2 do semiciclo negativo do conversor ponte-completa28           |

| Figura 10 - Etapa 3 do semiciclo negativo do conversor ponte-completa29          |

| Figura 11 - Etapa 4 do semiciclo negativo do conversor ponte-completa29          |

| Figura 12 - Modulação por largura de pulso30                                     |

| Figura 13 - Chaveamento resultante da comparação entre portadora e modulante .31 |

| Figura 14 - Princípio da Modulação Senoidal31                                    |

| Figura 15 - Chaveamento resultante da comparação entre portadora e modulante .32 |

| Figura 16 - Modulação PWM a três níveis33                                        |

| Figura 17 - Forma resultante da comparação entre triangular e vseno134           |

| Figura 18 - Forma resultante da comparação entre triangular e vseno235           |

| Figura 19 - Forma de onda da tensão de saída35                                   |

| Figura 20 - Diagrama de blocos para referência de corrente37                     |

| Figura 21 – Carga eletrônica com topologia back-to-back                          |

| Figura 22 – Sistema de malha fechada com compensador39                           |

| Figura 23 - Resposta ao degrau do sistema não compensado e compensado com        |

| PD40                                                                             |

| Figura 24 – Diagrama de blocos do compensador PD40                               |

| Figura 25 – Resposta ao degrau do sistema não compensado e compensado com Pl.    |

| 41                                                                               |

| Figura 26 – Diagrama de blocos do compensador PI42                               |

| Figura 27 - Resposta ao degrau do sistema não compensado e compensado com        |

| PD e PID43                                                                       |

| Figura 28 – Diagrama de blocos do compensador PID44                              |

| Figura 29 – Compensador PI discretizado45                                        |

| Figura 30 – Controlador Repetitivo4                                               | ١6         |

|-----------------------------------------------------------------------------------|------------|

| Figura 31 – Controlador repetitivo com proporcional em paralelo4                  | ŀ7         |

| Figura 32 – Diagrama do Simulink da geração de referência de corrente para a rede | e.         |

| 4                                                                                 | ١9         |

| Figura 33 – Diagrama do Simulink do atraso de fase da tensão do barramento5       | 50         |

| Figura 34 – Diagrama do Simulink do PI de corrente de entrada5                    | 50         |

| Figura 35 – Diagrama do Simulink do feed-forward5                                 | 51         |

| Figura 36 – Diagrama do <i>Simulink</i> da geração de PWM5                        | 51         |

| Figura 37 – Inversor de entrada5                                                  | 52         |

| Figura 38 – Diagrama do Simulink da geração de referência de corrente da carga5   | 53         |

| Figura 39 – Fluxograma da geração da corrente não linear5                         | 53         |

| Figura 40 – Diagrama lógico do Simulink para geração da referência de corrent     | te         |

| não-linear5                                                                       | 54         |

| Figura 41 – Diagrama do Simulink do controle repetitivo5                          | 56         |

| Figura 42 – Diagrama do Simulink da geração do PWM da carga eletrônica5           | 56         |

| Figura 43 – Inversor da carga eletrônica5                                         | 57         |

| Figura 44 – Sinais resultantes da simulação de carga linear. Acima: tensão d      | le         |

| entrada (Volts); abaixo: corrente de entrada (Amperes)5                           | 57         |

| Figura 45 - Referência de corrente (Pesos) e corrente da carga linear (Amperes) e | m          |

| regime permanente5                                                                | 58         |

| Figura 46 – Sinais resultantes da simulação de carga não-linear. Acima: tensão o  | ek         |

| entrada (Volts); abaixo: corrente de entrada (Amperes)5                           | 58         |

| Figura 47 - Referência de corrente (Pesos) e corrente da carga não-linea          | ar         |

| (Amperes) em regime permanente5                                                   | 59         |

| Figura 48 – Placa montada da carga eletrônica6                                    | 30         |

| Figura 49 – Dimensionamento do indutor a vazio6                                   | 3          |

| Figura 50 - Dimensionamento do indutor com carga6                                 | 3          |

| Figura 51 – <i>Software</i> de configuração da carga eletrônica7                  | '1         |

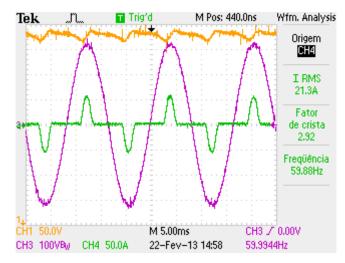

| Figura 52 – Sinal do <i>gate</i> (verde) e do coletor (roxo) do IGBT7             | '2         |

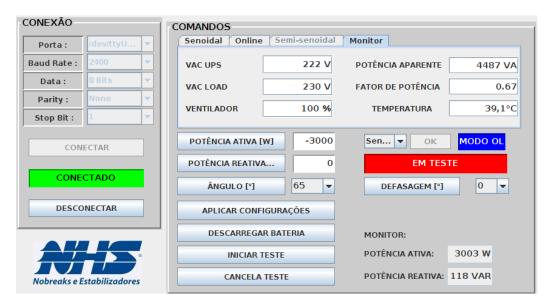

| Figura 53 – Configuração do Software para a simulação de carga linear7            | '3         |

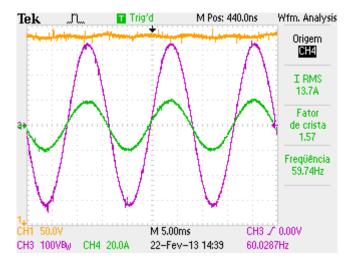

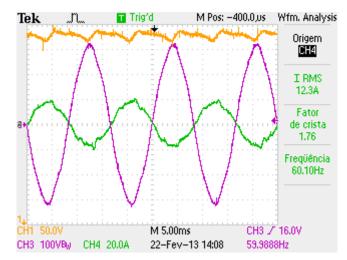

| Figura 54 - Aquisição da tensão do barramento (amarelo), tensão (roxo) e corrent  | te         |

| (verde) do UPS durante o teste de corrente linear7                                | ′3         |

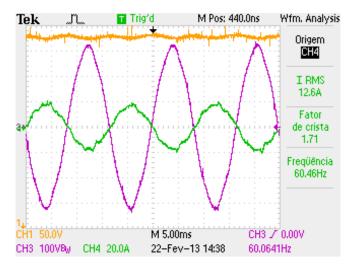

| Figura 55 - Aquisição da tensão do barramento (amarelo), tensão (roxo) e corrent  | te         |

| (verde) da rede durante o teste de corrente linear7                               | <b>'</b> 4 |

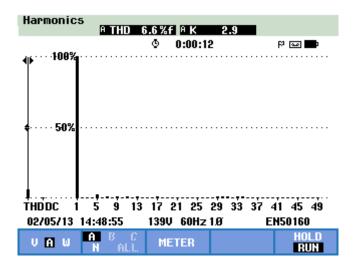

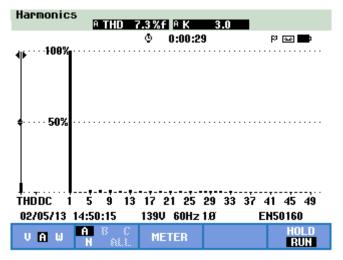

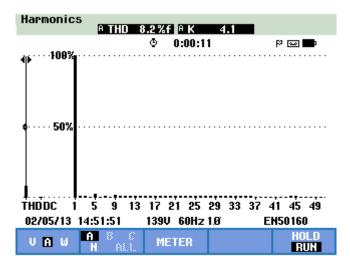

| Figura 56 – THDi da corrente devolvida à rede com o UPS conectado na rede (teste  |

|-----------------------------------------------------------------------------------|

| linear)74                                                                         |

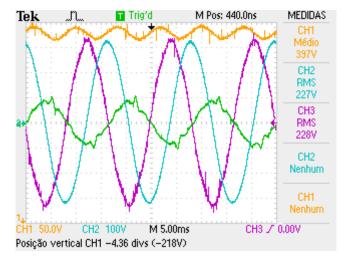

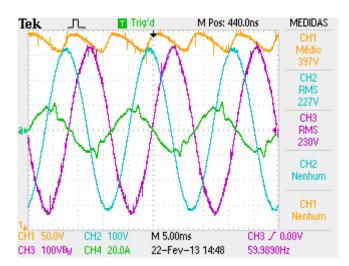

| Figura 57 – Aquisição da tensão do barramento (amarelo), tensão (roxo) e corrente |

| (verde) da rede e tensão do UPS (azul) durante o teste de corrente linear com UPS |

| desconectado da rede75                                                            |

| Figura 58 - THDi da corrente devolvida à rede com o UPS desconectado da rede      |

| (teste linear)                                                                    |

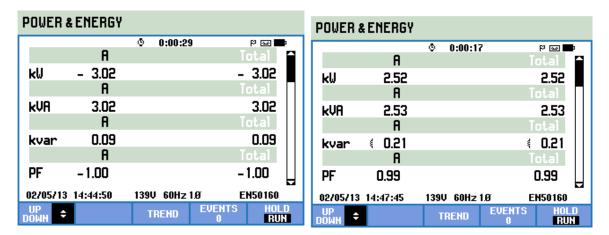

| Figura 59 – Potência drenada do UPS (esq.) e potência devolvida à rede (dir.) no  |

| teste de carga linear76                                                           |

| Figura 60 – Configuração do <i>Software</i> para a simulação de carga linear76    |

| Figura 61 – Aquisição da tensão do barramento (amarelo), tensão (roxo) e corrente |

| (verde) do UPS durante o teste de corrente não-linear77                           |

| Figura 62 – Aquisição da tensão do barramento (amarelo), tensão (roxo) e corrente |

| (verde) da rede durante o teste de corrente não-linear77                          |

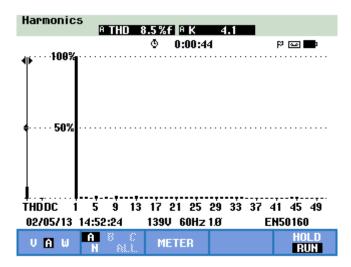

| Figura 63 – THDi da corrente devolvida à rede com o UPS conectado na rede (teste  |

| não-linear)78                                                                     |

| Figura 64 – Aquisição da tensão do barramento (amarelo), tensão (roxo) e corrente |

| (verde) da rede e tensão do UPS (azul) durante o teste de corrente não-linear com |

| UPS desconectado da rede78                                                        |

| Figura 65 – THDi da corrente devolvida à rede com o UPS desconectado da rede      |

| (teste não-linear)79                                                              |

| Figura 66 – Simulação de carga linear com achatamento na tensão80                 |

## **LISTA DE SIGLAS**

ADC Analog-to Digital Converster

CA Corrente Alternada

CC Corrente Contínua

DSP Digital Signal Processor

FIR Finite Impulse Response

IGBT Insulated Gate Bipolar Transistor

PD Proporcional Derivativo

PI Proporcional Integral

PID Proporcional Integral e Derivativo

PWM Pulse Width Modulation

RMS Root Mean Square

UPS Uninterruptable Power Systems

THDi Taxa de distorção harmônica de corrente

## **LISTA DE SÍMBOLOS**

V<sub>ab</sub> Tensão entre terminais do inversor ponte-completa

$S_1$ ,  $S_2$ ,  $S_3$ ,  $S_4$  Chave do inversor ponte-completa

N Relação entre frequências portadora e moduladora

T Período de onda

T<sub>p</sub> Período da onda portadora

f Frequência de onda

$f_p$  Frequência de onda portadora

M Índice de modulação

$V_1$  Amplitude de onda moduladora

$V_2$  Amplitude de onda portadora

$V_{O1MAX}$  Amplitude da componente fundamental da tensão de saída

V<sub>O1ef</sub> Valor eficaz da componente fundamental da tensão de saída

E Tensão da fonte de entrada

*V*<sub>seno1</sub> Primeira onda moduladora senoidal

*V*<sub>seno2</sub> Segunda onda moduladora senoidal

*v<sub>tri</sub>* Onda portadora triangular

+  $V_d$  Nível positivo de tensão de saída para conversor utilizando

modulação por largura de pulso

-  $V_d$  Nível negativo de tensão de saída para conversor utilizando

modulação por largura de pulso

Q<sub>1</sub>, Q<sub>2</sub>, Q<sub>3</sub>, Q<sub>4</sub>, Chave do conversor CC

$G_c(s)$  Compensador

G(s) Planta de Controle

H(s) Realimentação do Sistema

$f_Z$  Frequência do zero do compensador

*f<sub>c</sub>* Frequência de Cruzamento

$K_1$  Ganho proporcional

$K_2$  Ganho integral

$K_3$  Ganho derivativo

$K_P$  Ganho proporcional

$K_l$  Ganho integral

T<sub>s</sub> Período de chaveamento

$F_1(z)$  Filtro do controle repetitivo  $F_2(z)$  Filtro do controle repetitivo

*Iref*<sub>rede</sub> Corrente de referência da rede

Vrede<sub>cont</sub> Amostra de tensão da rede utilizada para o controle

PI<sub>Vbus</sub> PI de tensão do barramento

Vrede<sub>RMS</sub> Valor eficaz da tensão da rede

$V_{RMS}$  Valor eficaz de tensão

Vbus<sub>norm</sub> Tensão do barramento normalizada

zero<sub>bus</sub> Zero do controlador em atraso de fase da tensão do

barramento

Iref<sub>Load</sub> Corrente de referência da saída da UPS

*Vups*<sub>cont</sub> Amostra de tensão da UPS utilizada para controle

Vups<sub>RMS</sub> Valor eficaz da tensão da UPS

Potência Potência utilizada para teste da UPS

*urp* Controlador repetitivo

*u*<sub>bus</sub> Controlador do barramento

*e*<sub>bus</sub> Erro do barramento

*u*<sub>rede</sub> Controlador da rede

*e*<sub>rede</sub> Erro da rede

$u_{pot}$  Controlador da potência

*e*<sub>pot</sub> Erro da potência

V<sub>bus</sub> Tensão do barramento

*V*<sub>bus-min</sub> Tensão mínima do barramento

*f<sub>in</sub>* Frequência de entrada do conversor

P Potência

C Capacitância

L Indutância

V Tensão

I Corrente

A<sub>TR</sub> Área da perna central do transformador

$B_{TR}$  Fluxo magnético

*n* Número de espiras

$V_{TR}$  Tensão aplicada nos terminais do transformador

ω<sub>c</sub> Frequência angular de corte

$V_{CE}$  Tensão entre coletor e emissor

*I<sub>CE</sub>* Corrente entre coletor e emissor

V<sub>GE</sub> Tensão entre *gate* e emissor

*I<sub>Máx</sub>* Corrente máxima

*I<sub>Pico-Máx</sub>* Corrente máxima de pico

R Resistência

Tempo de condução do snubber.

Lag Atraso do controle repetitivo

*f*<sub>rep</sub> Frequência do compensador repetitivo

$\varphi_{LC}$  Período do filtro LC

# SUMÁRIO

| LISTA DE FIGURAS                                       | 2  |

|--------------------------------------------------------|----|

| LISTA DE SIGLAS                                        | 10 |

| LISTA DE SÍMBOLOS                                      | 11 |

| 1 INTRODUÇÃO                                           | 17 |

| 1.1 TEMA                                               | 17 |

| 1.1.1 Delimitação do tema                              | 17 |

| 1.2 PROBLEMAS E PREMISSAS                              | 19 |

| 1.3 OBJETIVOS                                          | 19 |

| 1.3.1 Objetivos gerais                                 | 19 |

| 1.3.2 Objetivos específicos                            | 19 |

| 1.4 JUSTIFICATIVA                                      | 20 |

| 1.5 PROCEDIMENTOS METODOLÓGICOS                        | 21 |

| 1.6 ESTRUTURA DO TRABALHO                              | 22 |

| 2 REVISÃO BIBLIOGRÁFICA                                | 23 |

| 2.1 CONVERSORES CC-CA                                  | 23 |

| 2.1.1 Conversor Ponte-Completa                         | 23 |

| 2.1.1.1 Etapas de Operação do Conversor Ponte-Completa | 24 |

| 2.1.1.1.1 Etapa 1 do Semiciclo Positivo                | 25 |

| 2.1.1.1.2 Etapa 2 do Semiciclo Positivo                | 25 |

| 2.1.1.1.3 Etapa 3 do Semiciclo Positivo                | 26 |

| 2.1.1.1.4 Etapa 4 do Semiciclo Positivo                | 27 |

| 2.1.1.1.5 Etapa 1 do Semiciclo Negativo                | 27 |

| 2.1.1.1.6 Etapa 2 do Semiciclo Negativo                | 28 |

| 2.1.1.1.7 Etapa 3 do Semiciclo Negativo                | 29 |

| 2.1.1.1.8 Etapa 4 do Semiciclo Negativo                | 29 |

| 2.2 MODULAÇÃO POR LARGURA DE PULSO                                           | 30 |

|------------------------------------------------------------------------------|----|

| 2.2.1 Modulação por Largura de Pulsos Senoidal                               | 31 |

| 2.2.1.1 Modulação por Largura de Pulsos Senoidal a Três Níveis               | 33 |

| 2.3 CONTROLE DE CORRENTE                                                     | 36 |

| 2.5 CARGA ELETRÔNICA                                                         | 37 |

| 2.5.1 Carga Eletrônica CA                                                    | 37 |

| 2.6 COMPENSADORES                                                            | 39 |

| 2.6.1 Compensador Proporcional Derivativo (Avanço de Fase)                   | 39 |

| 2.6.2 Compensador Proporcional Integral (Atraso de Fase)                     | 41 |

| 2.6.3 Compensador Proporcional Integral Derivativo (Atraso e Avanço de Fase) | 43 |

| 2.7 DISCRETIZAÇÃO DO CONTROLADOR PI                                          | 44 |

| 2.8 CONTROLADOR REPETITIVO                                                   | 46 |

| 3 DESENVOLVIMENTO                                                            | 48 |

| 3.1 SIMULAÇÃO                                                                | 48 |

| 3.1.1 Conversor da rede                                                      | 48 |

| 3.1.1.1 Geração da referência de corrente                                    | 48 |

| 3.1.1.2 Feed-forward                                                         | 50 |

| 3.1.1.3 Geração do PWM                                                       | 51 |

| 3.1.2 Conversor do UPS                                                       | 52 |

| 3.1.2.1 Geração da referência de corrente                                    | 52 |

| 3.1.2.2 Controle de corrente                                                 | 54 |

| 3.1.2.3 Geração do PWM                                                       | 56 |

| 3.1.3 Resultados                                                             | 57 |

| 3.1.4 Conclusão                                                              | 59 |

| 3.2 IMPLEMENTAÇÃO FÍSICA                                                     | 60 |

| 3.2.1 Dimensionamento                                                        | 60 |

| 3.2.1.1 Capacitor do barramento                                              | 60 |

| 3.2.1.2 Dimensionamento dos indutores                             | 61 |

|-------------------------------------------------------------------|----|

| 3.2.1.3 Dimensionamento do capacitor                              | 64 |

| 3.2.1.4 Dimensionamento das chaves semicondutoras                 | 64 |

| 3.2.1.5 Acionamento das chaves semicondutoras                     | 65 |

| 3.2.1.6 Dimensionamento do transformador                          | 66 |

| 3.2.2 Desenvolvimento do firmware                                 | 67 |

| 3.2.2.1 Controle do barramento compartilhado                      | 68 |

| 3.2.2.2 Controle de corrente da rede                              | 68 |

| 3.2.2.3 Controle de corrente do UPS                               | 69 |

| 3.2.3 Software de configuração da carga eletrônica                | 70 |

| 3.2.4 Resultados                                                  | 72 |

| 3.2.4.1 Chaveamento dos IGBTs                                     | 72 |

| 3.2.4.2 Simulação de corrente linear                              | 72 |

| 3.2.4.3 Simulação de corrente não-linear                          | 76 |

| 3.2.4.4 Simulação de carga linear quando há afundamento de tensão | 80 |

| 4 CONSIDERAÇÕES FINAIS                                            | 81 |

| 5 REFERÊNCIAS                                                     | 82 |

| APÊNDICE A                                                        | 85 |

# 1 INTRODUÇÃO

#### **1.1 TEMA**

Com o aumento no número de indústrias e demandas por produtos no mercado, o consumo energético no mundo tende apenas a subir. O modo mais atraente de amenizar os danos que tal demanda pode causar é aplicando os conceitos de sustentabilidade. Com isto em mente, várias empresas no mundo estão utilizando as cargas eletrônicas pela sua capacidade de regeneração da energia, utilizada no teste de volta para a rede elétrica.

### 1.1.1 Delimitação do tema

Segundo Wang (2009), a carga eletrônica é um instrumento de eletrônica de potência cuja finalidade é simular cargas tais como resistores, indutores e capacitores. Em testes de potência convencionais, utilizando resistores, a energia utilizada é totalmente desperdiçada, além de aquecer o local do teste, tornando-o desagradável em algumas situações. Além da simulação de cargas, este dispositivo tem a capacidade de devolver para a rede elétrica grande parte da energia utilizada nos testes, evitando o desperdício de energia (LI, 2009).

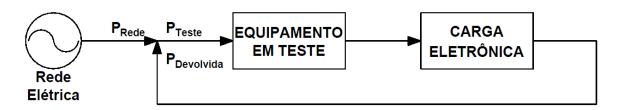

Figura 1 – Diagrama de blocos da carga eletrônica.

Fonte: Adaptado de Li (2008, p. 630)

Como visto em Huilin (2004), sua utilização na realização de testes de *burn- in* e de desgaste em inversores, unidades ininterruptas de energia (UPS - do inglês

Uninterruptible Power Supply), geradores e afins está cada vez maior, pois a carga eletrônica pode proporcionar testes de tensão constante, corrente constante ou potência constante. Neste projeto a carga eletrônica proposta será utilizada para testes em UPS.

Com as várias pesquisas na área, hoje é possível projetar cargas com regeneração de corrente senoidal, dupla conversão, regulagem do barramento CC e harmônicos de baixa amplitude.

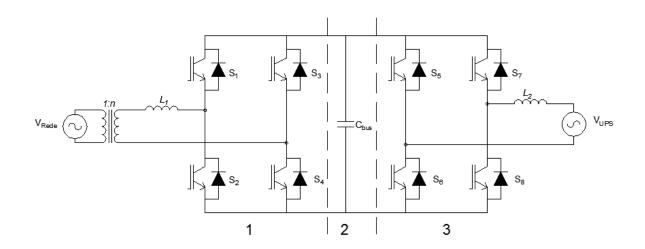

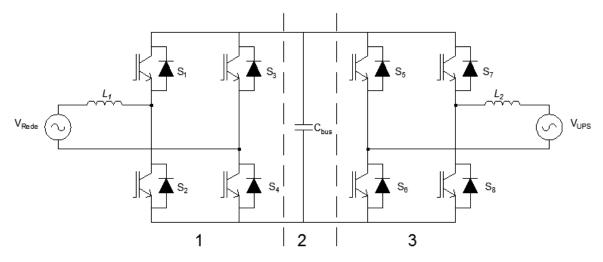

A topologia de carga eletrônica que será desenvolvida é a *back-to-back*. Esta topologia possui dois conversores *full-bridge* (ponte-completa), como mostrado na Figura 2.

Figura 2 – Carga eletrônica com topologia back-to-back isolada da rede. Fonte: Adaptado de Li (2008, p. 631).

Esta topologia permite que a energia utilizada para o teste da UPS no conversor da terceira parte flua para a rede pelo conversor da primeira parte através do transformador isolador.

Se o UPS estiver utilizando energia da bateria, a carga eletrônica estará injetando energia à rede. Caso esteja conectado à rede, a carga estará apenas devolvendo parte da energia utilizada.

Para que a carga eletrônica esteja isolada da rede, utiliza-se um transformador com relação de espiras unitárias entre a carga e a rede.

#### 1.2 PROBLEMAS E PREMISSAS

A dificuldade na implementação de uma carga eletrônica está na concordância entre os vários controles existentes. Cada etapa dos conversores possui seu controle e estes influenciam um nos outros, complicando a operação ótima do sistema. Com um controle projetado erroneamente, é possível que a referência de corrente não seja corretamente replicada, podendo gerar erros nos valores desejados de potência ou deformações na forma de onda e, assim, acabar por comprometer o objetivo do teste aplicado pela carga.

#### 1.3 OBJETIVOS

## 1.3.1 Objetivos gerais

Desenvolver uma carga eletrônica isolada com controle de potência, controle de forma de onda de corrente e regeneração da energia utilizada para a rede com forma de onda de corrente senoidal.

#### 1.3.2 Objetivos específicos

Como metas específicas para o projeto e implementação da carga eletrônica, tem-se:

- Desenvolver o circuito elétrico;

- Simular a carga eletrônica;

- Montar o protótipo;

- Desenvolver o *firmware*;

- Projetar os controladores;

- Ajustar os controles;

- Validar os resultados da simulação.

#### 1.4 JUSTIFICATIVA

Alguns produtos necessitam de testes que visam averiguar o desempenho fornecido pelo equipamento produzido aplicando cargas em sua saída. Este trabalho visa construir uma carga eletrônica, que torna possível que tais testes sejam realizados com o mínimo de desperdício de energia, ajudando a levar a frente a ideia da sustentabilidade. Fato que é possível devido à regeneração da energia à rede elétrica, apenas sendo desperdiçadas as perdas que ocorrem no chaveamento, no cobre e o consumo do próprio DSP e outros semicondutores presentes no circuito.

Sua aplicação vai desde baterias, conversores eletrônicos, fonte de tensão até geradores. Além disso, observa-se que é necessário um estudo aprofundado em eletrônica de potência e sistemas de controle, a fim de que o teste realizado forneça o resultado desejado.

Há vários métodos para a construção de uma carga eletrônica. Neste estudo, o enfoque será a construção de uma carga eletrônica através de conversores *full-bridge*, controle repetitivo, controle PI e avanço de fase, pois são métodos já conhecidos e que devem trazer uma maior eficácia para a construção da carga eletrônica.

No estudo, haverá o objetivo da construção de uma carga eletrônica que seja capaz de fornecer potência à rede elétrica, além de ser capaz de fornecer com forma de onda de corrente senoidal.

## 1.5 PROCEDIMENTOS METODOLÓGICOS

Como metodologia de estudo e implementação da carga eletrônica, será realizada a pesquisa teórica, a análise computacional e os experimentos práticos. A revisão bibliográfica utilizará como principais meios de informação os portais de periódicos científicos e a biblioteca da UTFPR. A análise computacional contará com o auxílio do programa computacional MATLAB. Para os experimentos práticos, será usado o laboratório da empresa NHS e a estrutura que este proporciona, como componentes eletrônicos, fontes de tensão e osciloscópios. Também serão realizados encontros periódicos com o professor orientador, para a obtenção de informações que auxiliem no estudo.

O estudo será dividido de acordo com as seguintes etapas:

- ETAPA 1: Elaboração do referencial teórico; com o auxílio dos meios de informação citados, pretende-se encontrar livros, artigos e demais arquivos que auxiliem na compreensão e aprofundamento sobre o tema:

- ETAPA 2: Estudo e desenvolvimento da simulação da carga eletrônica; será implementado um programa pelo MATLAB que simule o correto funcionamento da carga eletrônica;

- ETAPA 3: Estudo e desenvolvimento do protótipo da carga eletrônica;

- ETAPA 4: Obtenção dos dados do protótipo da carga eletrônica;

- ETAPA 5: Validação dos resultados teóricos; após obtenção dos dados da carga eletrônica, os resultados teóricos serão comparados com os dados experimentais para avaliar a eficácia da carga eletrônica.

- ETAPA 6: Conclusões; realização de um estudo para avaliar se a carga eletrônica proposta correspondeu ao esperado, proporcionando controle e formas de onda de acordo com o proposto.

#### 1.6 ESTRUTURA DO TRABALHO

O trabalho será documentado em cinco capítulos. O primeiro capítulo apresentará a delimitação do tema, assim como os problemas, premissas, objetivos e a metodologia referentes ao estudo do tema.

No segundo capítulo se encontrará a base teórica para a realização da carga eletrônica, principalmente focada na obtenção de referencial bibliográfico sobre o conversor ponte-completa, controle proporcional, derivativo e integral, discretização de controle e controlador repetitivo.

No terceiro capítulo será apresentada a fase de construção da simulação da carga eletrônica através do programa MATLAB.

Os resultados experimentais serão expostos no capítulo quatro, para que se tenha a comparação e a esperada validação dos dados obtidos da carga eletrônica proposta.

O quinto e último capítulo avaliará a eficácia e viabilidade da carga eletrônica proposta.

## 2 REVISÃO BIBLIOGRÁFICA

#### 2.1 CONVERSORES CC-CA

Os conversores CC-CA, também conhecidos como inversores, possuem a função básica de converter uma fonte contínua (de tensão ou de corrente) aplicada à sua entrada, em uma fonte alternada, de valor médio nulo, simétrica em amplitude e frequência constante (BARBI, 2008, p.1).

Os inversores possuem diversas características que diferenciam cada topologia de conversor CC-CA, sendo que as topologias são utilizadas de acordo com a necessidade da aplicação. As topologias mais utilizadas são *half-bridge* (meia-ponte), *full-bridge* (ponte-completa) e *push-pull*.

Os conversores CC-CA podem ser monofásicos, trifásicos ou possuir mais fases, ser isolados ou não isolados, ser inversores de corrente ou de tensão, além de poderem atuar em diferentes modos de condução.

As aplicações dos conversores CC-CA são variadas, como na sua utilização para o controle de velocidade de motores de corrente alternada, sistemas ininterruptos de energia e sistemas de alimentação embarcados (GUERREIRO; MUHLEN; POMILIO, 2012, p.1).

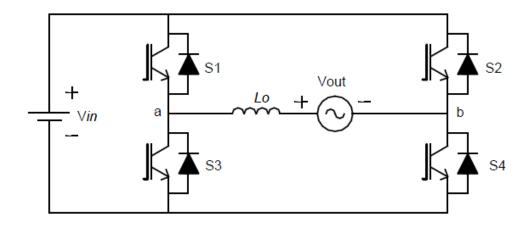

A topologia a ser utilizada para o estudo é a de um inversor monofásico ponte-completa, pois este conversor é indicado para grandes potências e altas tensões de saída. O inversor ponte-completa utilizará o chaveamento dos dispositivos semicondutores através da modulação por largura de pulso (PWM - do inglês *Pulse Width Modulation*), como explicado no capítulo 2.2.

## 2.1.1 Conversor Ponte-Completa

A estrutura do conversor CC-CA em ponte completa, ou inversor pontecompleta, representada na Figura 3, possui dois braços compostos por um par de chaves cada uma possuindo um diodo antiparalelo.

Figura 3 - Conversor CC-CA em ponte completa Fonte: Adaptado de Pinheiro Filho (2005, p. 40).

O inversor ponte-completa apresenta os menores esforços de tensão e corrente nas chaves comandadas se comparado com as topologias meia-ponte e push-pull (BARBI; DENIZAR, 2008, p.22).

Para o comando das chaves, foi escolhida a utilização da modulação PWM de três níveis em alta frequência, para que o conteúdo harmônico possua frequência que se distancie do termo fundamental (BARBI; DENIZAR, 2008, p.22).

## 2.1.1.1 Etapas de Operação do Conversor Ponte-Completa

Quando em modo contínuo e fornecendo energia para a rede, o conversor CC-CA ponte-completa possui 8 etapas de operação, onde 4 etapas estão no semiciclo positivo da tensão de saída e 4 etapas no semiciclo negativo da tensão de saída (PINHEIRO FILHO, 2005, p.40).

#### 2.1.1.1.1 Etapa 1 do Semiciclo Positivo

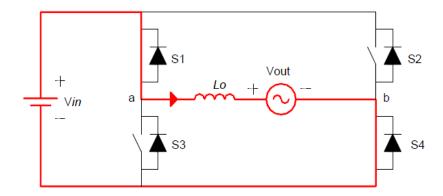

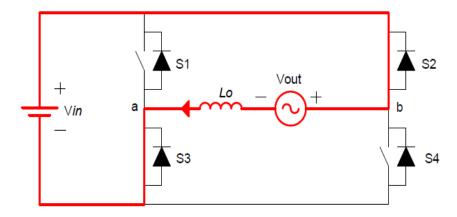

Figura 4 - Etapa 1 do semiciclo positivo do conversor ponte-completa Fonte: Adaptado de Pinheiro Filho (2005, p. 43).

Na primeira etapa do conversor ponte-completa, representada pela Figura 4, as chaves  $S_1$  e  $S_4$  estão conduzindo. A tensão na fonte CC é maior do que a tensão aplicada da rede, portanto a corrente possui o sentido da seta da Figura 4 e valor crescente.

A primeira etapa termina quando a chave S<sub>4</sub> é acionada para interromper a condução, iniciando a Etapa 2 (PINHEIRO FILHO, 2005, p.43).

## 2.1.1.1.2 Etapa 2 do Semiciclo Positivo

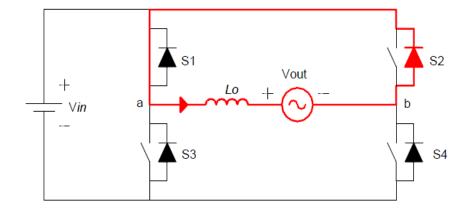

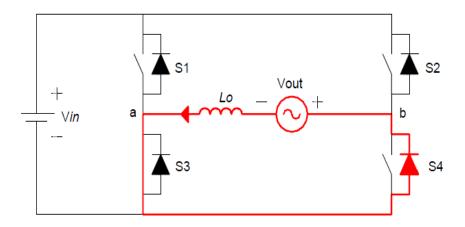

Figura 5 - Etapa 2 do semiciclo positivo do conversor ponte-completa Fonte: Adaptado de Pinheiro Filho (2005, p. 43).

A segunda etapa de funcionamento do conversor ponte-completa, representada na Figura 5, possui a chave  $S_1$  e o diodo antiparalelo da chave  $S_2$  conduzindo.

Nesta configuração, a corrente possui a direção indicada pela seta. Como não há tensão de entrada aplicada sobre o indutor e a carga, a tensão  $V_{ab}$  é nula e a corrente no indutor decresce linearmente (PINHEIRO FILHO, 2005, p.43).

## 2.1.1.1.3 Etapa 3 do Semiciclo Positivo

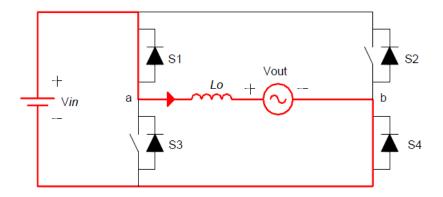

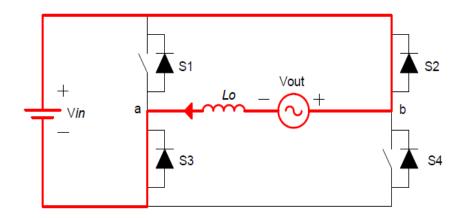

Figura 6 - Etapa 3 do semiciclo positivo do conversor ponte-completa Fonte: Adaptado de Pinheiro Filho (2005, p. 44).

A terceira etapa do conversor ponte-completa é similar a Etapa 1, como representado na Figura 6. A chave  $S_4$  assume a corrente do diodo da chave  $S_2$ , fazendo com que a tensão  $V_{ab}$  possua o valor da tensão de entrada positiva (PINHEIRO FILHO, 2005, p.44).

## 2.1.1.1.4 Etapa 4 do Semiciclo Positivo

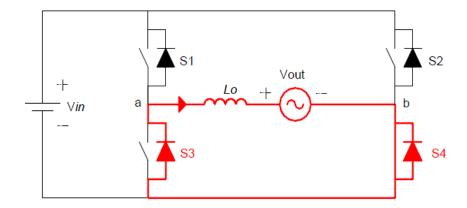

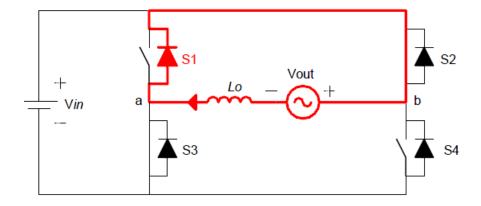

Figura 7 - Etapa 4 do semiciclo positivo do conversor ponte-completa Fonte: Adaptado de Pinheiro Filho (2005, p. 44).

Na Etapa 4 do conversor ponte-completa, representada na Figura 7, a chave  $S_1$  é comandada a interromper a condução, fazendo com que a corrente do indutor possua o caminho através da chave  $S_4$  e do diodo antiparalelo da chave  $S_3$ .

A tensão  $V_{ab}$  é nula, fazendo com que o indutor descarregue pela roda-livre e a corrente decresça linearmente (PINHEIRO FILHO, 2005, p.44).

## 2.1.1.1.5 Etapa 1 do Semiciclo Negativo

Figura 8 - Etapa 1 do semiciclo negativo do conversor ponte-completa Fonte: Adaptado de Pinheiro Filho (2005, p. 45).

Na Etapa 1 do semiciclo negativo do conversor ponte-completa, representada na Figura 8, as chaves  $S_2$  e  $S_4$  são comandadas a conduzir.

Nesta configuração a tensão  $V_{ab}$  é negativa, fazendo com que a corrente no indutor e carga tenha o sentido indicado pela seta e valor crescente, porém negativo (PINHEIRO FILHO, 2005, p.45).

## 2.1.1.1.6 Etapa 2 do Semiciclo Negativo

Figura 9 - Etapa 2 do semiciclo negativo do conversor ponte-completa Fonte: Adaptado de Pinheiro Filho (2005, p. 46).

A Etapa 2 de funcionamento do semiciclo negativo do conversor pontecompleta, representada na Figura 9, possui a chave  $S_3$  e o diodo antiparalelo da chave  $S_4$  conduzindo.

Neste estágio, a tensão  $V_{ab}$  é nula e a corrente no indutor decresce linearmente na direção indicada pela seta (PINHEIRO FILHO, 2005, p.46).

### 2.1.1.1.7 Etapa 3 do Semiciclo Negativo

Figura 10 - Etapa 3 do semiciclo negativo do conversor ponte-completa Fonte: Adaptado de Pinheiro Filho (2005, p. 46).

A terceira etapa do conversor ponte-completa é similar a Etapa 1, como representado na Figura 10. A chave  $S_3$  assume a corrente do indutor, fazendo com que a tensão  $V_{ab}$  possua valor negativo da tensão de entrada (PINHEIRO FILHO, 2005, p.46).

#### 2.1.1.1.8 Etapa 4 do Semiciclo Negativo

Figura 11 - Etapa 4 do semiciclo negativo do conversor ponte-completa Fonte: Adaptado de Pinheiro Filho (2005, p. 46).

Na quarta etapa do semiciclo negativo, mostrada na Figura 11, a chave  $S_3$  sofre bloqueio, fazendo com que  $S_1$  assuma a corrente. A chave  $S_1$  é então

comandada a conduzir, porém devido ao sentido da corrente, a corrente se mantém circulando pelo diodo antiparalelo (PINHEIRO FILHO, 2005, p.46).

# 2.2 MODULAÇÃO POR LARGURA DE PULSO

A modulação por largura de pulso tem sido alvo de frequentes estudos, usos e criação de novos métodos, como em sistemas de controle de velocidade de motores CC (LI; HUANG; YIN, 2008), controle de corrente de conversores fonte de tensão (WANG; LI, 2010) e no controle digital de inversores de UPS (DENG; ORUGANTI; SRINIVASAN, 2005).

Na modulação por largura de pulso, as chaves do conversor são ligadas e desligadas várias vezes durante um semiciclo e a tensão de saída é controlada pela variação da largura de pulsos (RASHID, 1999, p. 213).

A frequência em uma modulação por largura de pulso é constante, variandose o tempo que a chave permanece ligada (POMILIO, 2012, p.1).

O chaveamento é realizado através da comparação de um sinal de controle, chamado de modulante, com uma onda periódica, chamada de portadora (POMILIO, 2012, p.1).

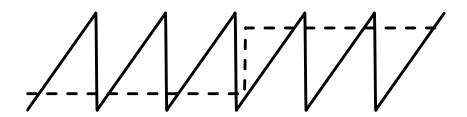

Na Figura 12 estão mostrados a portadora, uma onda periódica dente-deserra, assim como a modulante, representada através de linhas pontilhadas.

Figura 12 - Modulação por largura de pulso Fonte: Adaptado de Pomilio (2012, p.3-1)

Na Figura 13 está representado o chaveamento resultante da comparação linear entre a portadora e a modulante da Figura 12.

Figura 13 - Chaveamento resultante da comparação entre portadora e modulante Fonte: Adaptado de Pomilio (2012, p.3-1)

No estudo proposto, será realizada a modulação PWM senoidal, que reduz significativamente o fator de distorção e as componentes harmônicas em comparação com a modulação realizada através de comparação linear.

## 2.2.1 Modulação por Largura de Pulsos Senoidal

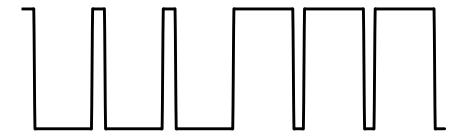

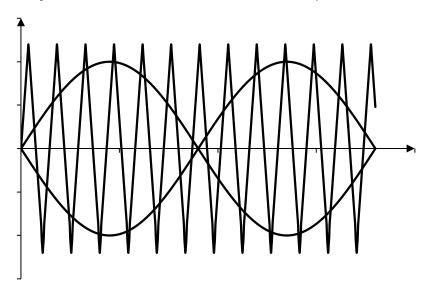

A modulação por largura de pulsos senoidal é realizada através da comparação de uma referência senoidal de baixa frequência com uma onda triangular de alta frequência, como mostrado na Figura 14 (BARBI; DENIZAR, 2008, p.332).

Figura 14 - Princípio da Modulação Senoidal Fonte: Adaptado de Barbi e Denizar (2008, p.333)

Através da intersecção das duas formas de onda é gerado o chaveamento resultante, como mostrado na Figura 15.

Figura 15 - Chaveamento resultante da comparação entre portadora e modulante Fonte: Adaptado de Barbi e Denizar (2008, p.333)

A variação dos pulsos gerada pelo chaveamento mostrado na Figura 15 resulta em uma onda senoidal na saída do conversor.

A frequência da componente fundamental da tensão de saída segue a frequência da onda moduladora senoidal, a frequência de comutação das chaves estáticas segue a onda portadora triangular.

A relação N entre as duas frequências é dada pela equação (1).

$$N = \frac{T}{T_p} = \frac{f_p}{2f} \tag{1}$$

Onde T é o período da moduladora,  $T_p$  é o período da portadora, f é a frequência da moduladora e  $f_p$  é a frequência da portadora.

O índice de modulação M é dado pela equação (2).

$$M = \frac{V_1}{V_2} \tag{2}$$

Onde  $V_1$  é a amplitude da moduladora e  $V_2$  é o valor de pico da portadora.

A amplitude  $V_{O1max}$  e o valor eficaz  $V_{O1ef}$  da componente fundamental da tensão de saída são controlados pelo índice M através das equações (3) e (4).

$$Vo_{1max} = ME$$

(3)

$$Vo_{1ef} = \frac{Vo_{1max}}{\sqrt{2}} \tag{4}$$

Onde *E* é a tensão da fonte de entrada (BARBI; DENIZAR, 2008, p.334). Há duas formas de modulação PWM senoidal:

- Modulação PWM senoidal a dois níveis;

- Modulação PWM senoidal a três níveis.

A forma utilizada no estudo será a modulação PWM a três níveis.

## 2.2.1.1 Modulação por Largura de Pulsos Senoidal a Três Níveis

A modulação PWM senoidal a três níveis está representada na Figura 16.

Figura 16 - Modulação PWM a três níveis Fonte: Adaptado de Barbi e Denizar (2008, p.340)

De acordo com Barbi e Denizar (2008, p.338), "os sinais de comando são obtidos a partir da intersecção de duas ondas moduladas senoidais de mesma amplitude e frequência, mas defasadas de 180º uma em relação à outra, com uma onda portadora triangular".

Sendo  $v_{seno1}$  e  $v_{seno2}$  as ondas moduladoras senoidais e  $v_{tri}$  a onda portadora triangular, dadas pela Figura 16, será feita comparação entre as duas ondas senoidais para o chaveamento do conversor.

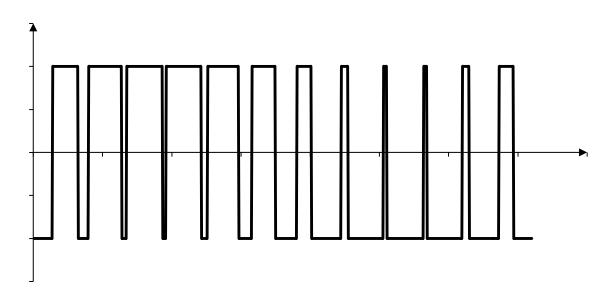

A comparação entre a onda triangular e a  $v_{seno1}$  que resulta o comando das chaves  $S_1$  e  $S_3$  de um conversor ponte-completa está mostrada na Figura 17.

Figura 17 - Forma resultante da comparação entre triangular e vseno1 Fonte: Adaptado de Barbi e Denizar (2008, p.340)

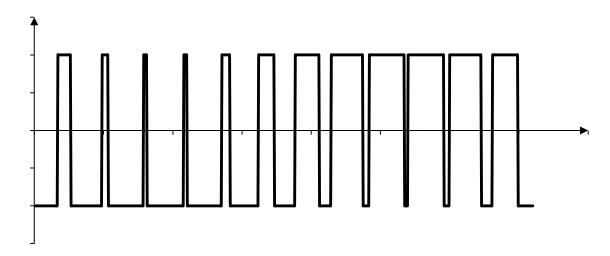

A comparação entre a onda triangular e a  $v_{seno2}$  que resulta no comando das chaves  $S_2$  e  $S_4$  está mostrada na Figura 18.

Considerando-se que as chaves  $S_1$  e  $S_2$  e as chaves  $S_3$  e  $S_4$  não podem conduzir simultaneamente, se  $v_{seno1} > v_{tri}$  a chave  $S_1$  entra em condução, se  $v_{seno2} < v_{tri}$  então a chave  $S_3$  entra em condução. Se  $v_{seno2} > v_{tri}$  a chave  $S_2$  entra em condução e se  $v_{seno2} < v_{tri}$  então a chave  $S_4$  entra em condução.

Figura 18 - Forma resultante da comparação entre triangular e vseno2 Fonte: Adaptado de Barbi e Denizar (2008, p.340)

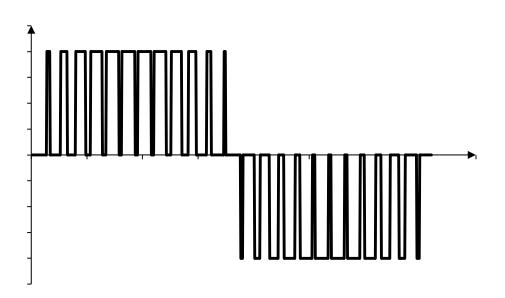

Desta forma, tem-se o chaveamento resultante para que a tensão de saída possua forma senoidal, mostrado na Figura 19.

Figura 19 - Forma de onda da tensão de saída Fonte: Adaptado de Barbi e Denizar (2008, p.340)

Nesta forma de esquema PWM, quando uma troca ocorre, a tensão de saída muda entre os níveis de tensão zero e  $+V_d$  ou entre zero e  $-V_d$ . Por esta razão, esta forma de esquema PWM é chamada de PWM senoidal a três níveis.

Utilizando a modulação PWM senoidal a três níveis se tem a vantagem de que a frequência é elevada, fazendo com que as componentes harmônicas tenham frequências mais elevadas, facilitando a filtragem.

Como desvantagem se tem as perdas por comutação das chaves, devido à frequência elevada de chaveamento (BARBI; DENIZAR, 2008, p.339)

#### 2.3 CONTROLE DE CORRENTE

O princípio de funcionamento do controle de corrente é fazer com que a corrente a ser entregue à rede e a corrente da saída da UPS tenham as formas de onda desejadas.

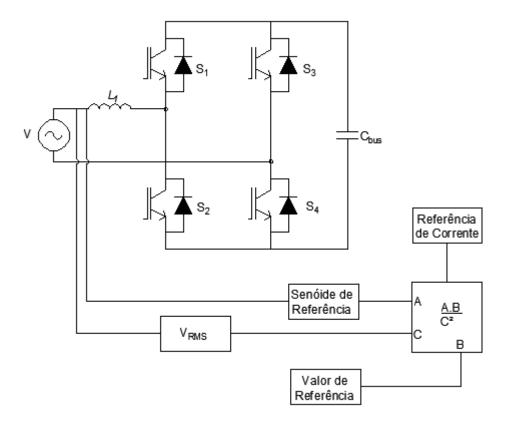

O funcionamento do circuito de controle de corrente típico aplicado em conversores está representado na Figura 20. Segundo Pomílio (2012, 3-10), a corrente no indutor do conversor é regulada de acordo com a referência gerada. Gera-se um sinal que determina a largura de pulso para que a corrente possua a forma desejada.

Na Figura 20, para os conversores utilizados na carga eletrônica, A é a amostra de tensão utilizada como referência de senóide, B é o valor de referência da tensão do barramento e C é o valor eficaz da amostra da tensão.

A referência de corrente, utilizada no controle de corrente, é então regulada de acordo com o valor dado pelo bloco A.B/C<sup>2</sup> e depois utilizada para a modulação de largura de pulso gerada no conversor.

A divisão de A por C realiza a divisão do sinal pelo módulo, retornando um valor unitário utilizado como referência. O valor de B é referente a um valor de potência, que dividido por C fornece uma amplitude de corrente. Portanto, tem-se um sinal de referência e uma amplitude de corrente que fornecem a referência de corrente desejada.

O conversor da rede requer uma referência de corrente que forneça corrente senoidal à rede. A referência de corrente do conversor da UPS é realizada para que a corrente na saída da UPS possua forma linear ou não-linear de acordo com a potência e ângulos requeridos.

Figura 20 - Diagrama de blocos para referência de corrente Fonte: Adaptado de Pomilio (2012, 3-10)

## 2.5 CARGA ELETRÔNICA

A carga eletrônica pode operar em modo de corrente contínua (CC) ou de corrente alternada (CA). Neste capítulo será apresentada a topologia da carga eletrônica que será utilizada neste projeto tal como sua justificativa.

## 2.5.1 Carga Eletrônica CA

A topologia mais comum para o desenvolvimento da carga eletrônica CA é a back-to-back (JEONG, 2010; LI, 2008), visto que esta realiza um conversão CA/CC e CC/CA, permitindo a operação da carga e do equipamento em teste em frequências e fases diferentes.

A Figura 1 mostra o diagrama de blocos de uma carga eletrônica CA com capacidade de regeneração de energia. A energia, que a carga eletrônica absorve do equipamento em teste, é devolvida para a rede, diminuindo a energia consumida (LI, 2008, p. 630).

Neste trabalho, propõe-se a implementação de uma carga eletrônica com topologia apresentada na Figura 28.

Figura 21 – Carga eletrônica com topologia *back-to-back*. Fonte: Adaptado de Li (2008, p. 631).

A secção 1 representa o inversor ponte completa responsável pelo controle da corrente de rede, e a secção 3 ilustra o inversor que será conectado ao equipamento a ser testado. A secção 2 apresenta o barramento CC compartilhado por ambos os lados. Tal barramento é responsável pela transferência de energia entre as duas partes (LI, 2008, p. 631), possibilitando a bidirecionalidade da carga eletrônica. Esta topologia permite, também, a inversão em frequências diferentes para cada conversor, possibilitando, assim, a operação da carga conectada à rede e o UPS operando em modo inversor. Nesta situação, o UPS estará trabalhando em uma frequência diferente da rede – mesmo que mínima – acarretando numa diferença de fase entre os dois conversores.

#### 2.6 COMPENSADORES

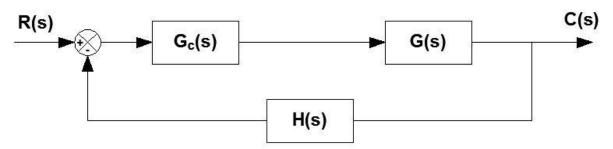

Para garantir a estabilidade da carga eletrônica, será necessário projetar compensadores para as diversas etapas. O projeto de controladores requer uma realimentação, que é comparada com uma referência gerando um erro. Partindo deste erro, o compensador atua na planta a fim de minimizar o erro, a oscilação da resposta transitória ou o tempo de assentamento. A ação mais comum dos compensadores na área da conversão de energia se dá por meio da variação da razão cíclica do PWM. No diagrama de blocos da Figura 22, G<sub>c</sub>(s) representa o compensador agindo na planta G(s) e H(s) é a realimentação do sistema.

Figura 22 – Sistema de malha fechada com compensador. Fonte: Ogata (2000, p. 542).

Os compensadores podem ser implementados de forma analógica ou digital. Neste capítulo serão apresentadas três estratégias de controle analógicas (PD, PI e PID), técnica de discretização e o controle repetitivo. Neste trabalho, serão utilizados compensadores digitais implementados em Processadores Digitais de Sinais (DSP – do inglês *Digital Signal Processor*).

### 2.6.1 Compensador Proporcional Derivativo (Avanço de Fase)

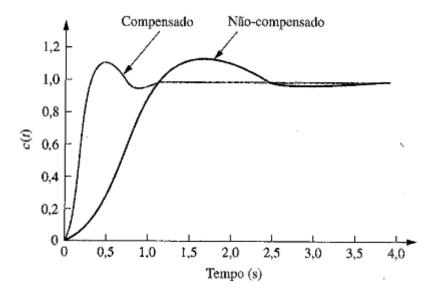

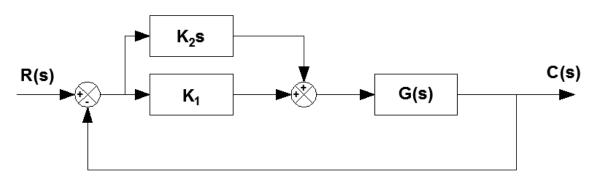

Segundo Nise (2002, p. 364), compensador PD tem por finalidade aumentar de forma ativa o amortecimento, reduzir as oscilações e sobressinal, aumentar a estabilidade e diminuir o tempo de assentamento, como mostrado na Figura 23. Porém, devido ao efeito derivativo, sua sensibilidade a ruídos é aumenta.

Figura 23 – Resposta ao degrau do sistema não compensado e compensado com PD.

Fonte: Nise (2002, p. 371).

Na Figura 24 está apresentado o diagrama de blocos do sistema compensado com PD

Figura 24 – Diagrama de blocos do compensador PD. Fonte: Nise (2002, p. 371).

Este compensador melhora a margem de fase adicionando um zero a uma frequência  $f_z$  distante o bastante da frequência de cruzamento  $f_c$ , de modo que a margem de fase seja aumentada ao nível desejado.

Uma vez projetado, o compensador PD pode ser implementado pela função transferência apresentada na equação (5) (NISE, 2002, p. 371).

$$G_C(s) = K_2 s + K_1 = K_2 \left( s + \frac{K_1}{K_2} \right)$$

(5)

Onde  $K_1$  representa o ganho proporcional e  $K_2$  representa o ganho derivativo.

Um efeito colateral indesejado que surge neste tipo de controlador é o aumento do ganho, de +20 dB/década, com a frequência. Para contornar este efeito, adicionam-se polos de alta frequência para que o ganho tenda a zero e atenuem os ruídos em tais bandas. Adicionando-se o polo, o controlador é chamado de compensador por avanço de fase.

Com o polo do compensador em avanço de fase mais afastado do eixo imaginário que o zero, a contribuição angular do compensador é positiva, exatamente como faz o zero de um compensador PD simples (NISE, 2002, p 372).

Deve-se, também, reservar uma atenção na frequência de chaveamento, uma vez que esta pode gerar um ganho no controlador se ela for mais alta que a frequência do polo (ERICKSON, 2004, p. 348-349).

### 2.6.2 Compensador Proporcional Integral (Atraso de Fase)

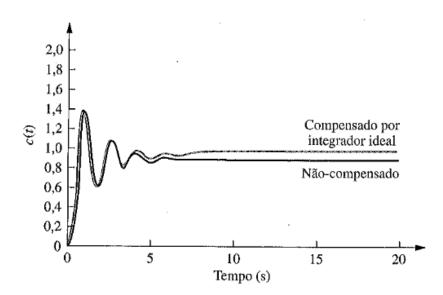

O compensador PI tem como principal característica a redução do erro de estado estacionário, para uma entrada degrau, sem afetar de forma significativa a resposta transitória, como pode ser visto na Figura 25.

Figura 25 – Resposta ao degrau do sistema não compensado e compensado com Pl. Fonte: Nise (2002, p. 359).

O diagrama de blocos apresentado na Figura 26 representa o sistema compensado com o PI.

Figura 26 – Diagrama de blocos do compensador Pl. Fonte: Nise (2002, p. 360).

A estratégia para a implementação do PI é a adição de um polo em zero, e de um zero próximo ao polo para que a contribuição do compensador calculada nos polos dominantes originais seja próxima de zero (NISE, 2002, p 358).

Com este tipo de compensador o ganho a baixas frequências é aumentado, melhorando a regulação para frequência bem abaixo da frequência de cruzamento. Devido a sua simplicidade e efetividade, o compensador PI é amplamente utilizado em sistemas com realimentação (ERICKSON, 2004, p. 351).

Depois de projetado, o compensador PI pode ser implementado segundo a equação (6) (NISE, 2002, p. 360).

$$G_{C}(s) = K_{1} + \frac{K_{2}}{s} = \frac{K_{1}\left(s + \frac{K_{2}}{K_{1}}\right)}{s}$$

$$\tag{6}$$

Onde  $K_1$  representa o ganho proporcional e  $K_2$  representa o ganho integral.

Posicionando-se o polo do compensador PI para a esquerda próximo à origem e a direita do zero do compensador, tem-se um compensador por atraso de fase.

Se o polo e o zero do compensador por atraso de faze estiverem próximos um do outro, a contribuição angular do compensador será aproximadamente zero, assim como no compensador PI.

Embora não aumente o tipo do sistema, o compensador por atraso de fase melhora efetivamente a constante de erro estático em relação a um sistema não compensado (NISE, 2002, p 361).

## 2.6.3 Compensador Proporcional Integral Derivativo (Atraso e Avanço de Fase)

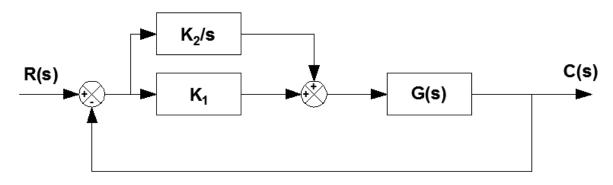

O compensador PID reúne as vantagens de cada ação de controle individual (OGATA, 2000, p.178). Em frequências baixas, o compensador integra o sinal de erro, conduzindo à uma regulação exata, e em frequências altas o compensador impõe um avanço de fase, proporcionando uma melhora na margem de fase (ERICKSON, 2004, p. 353).

Este controlador possui dois zeros e um polo na origem. Um zero e o polo na origem derivam do controlador PI, enquanto o outro zero provém do compensador PD (NISE, 2002, p. 376).

Figura 27 - Resposta ao degrau do sistema não compensado e compensado com PD e PID.

Fonte: Nise (2002, p. 379).

O diagrama de blocos do controlador PID pode ser representado como a Figura 28.

Figura 28 – Diagrama de blocos do compensador PID. Fonte: Nise (2002, p. 376).

Feito o projeto, a implementação é realizada de acordo com a equação (7) (NISE, 2002, p. 376).

$$G_{C}(s) = K_{1} + \frac{K_{2}}{s} + K_{3}s = \frac{K_{1}s + K_{2} + K_{3}s^{2}}{s} = \frac{K_{3}\left(s^{2} + \frac{K_{1}}{K_{3}}s + \frac{K_{2}}{K_{3}}\right)}{s}$$

(7)

Onde  $K_1$  representa o ganho proporcional,  $K_2$  o ganho integral e  $K_3$  o ganho derivativo.

Da mesma forma que o PID, a combinação entre o compensador por atraso de fase e o compensador por avanço de fase resulta em um compensador por avanço e atraso de fase, que melhora tanto a resposta transitória quanto o erro de estado estacionário (NISE, 2002, p. 380).

# 2.7 DISCRETIZAÇÃO DO CONTROLADOR PI

Para a implementação do controle em sistemas digitais, é necessário que se faça a discretização do plano *s* para o plano *z*. Neste trabalho, utilizaremos o método de integração de Euler em atraso. Para tal, a transformação de *s* para *z* respeita a equação (8) (BUSO, 2006).

$$s = \frac{z - 1}{z T_{S}} \tag{8}$$

A partir da equação (8), pode-se chegar ao formato da equação (9)

$$Gc(s) = K_{I} \frac{\left(1 + \frac{K_{P}}{K_{I}} s\right)}{s}$$

(9)

Substituindo (8) na equação (9), obtém-se a equação (10):

$$G_{C}(z) = K_{2} \frac{\left(1 + \frac{K_{P}}{K_{I}} \frac{z - 1}{z T_{S}}\right)}{\frac{z - 1}{z T_{S}}} = \frac{\left(K_{P} + K_{I} T_{S}\right) z - K_{P}}{z - 1} = K_{P} + K_{I} T_{S} \frac{z}{z - 1}$$

(10)

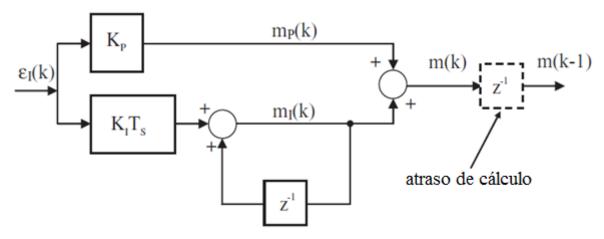

Figura 29 – Compensador PI discretizado Fonte: Buso (2006, p. 52).

A partir do diagrama de blocos apresentado na Figura 29, pode-se obter a equação (11). Tal equação pode ser facilmente utilizada no algoritmo a ser embarcado no DSP.

$$u(n) = K_P e(n) + K_I T_S e(n) + K_I T_S e(n-1)$$

(11)

### 2.8 CONTROLADOR REPETITIVO

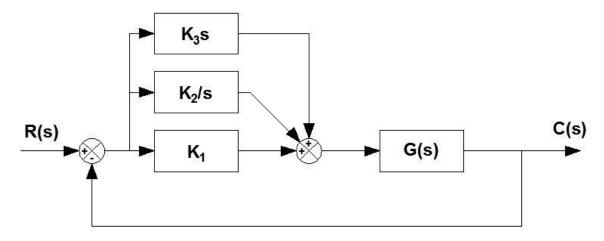

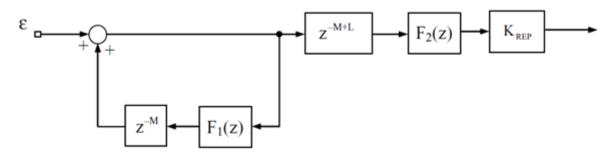

Neste trabalho será necessário fazer o controle de corrente de uma referência não-linear. Devido as suas derivadas, o controlador PI não consegue compensar o erro de forma satisfatória. Então, propõe-se o uso do controlador repetitivo que tem a propriedade de seguir qualquer dada referência com erro de regime zero (BUSO, 2006, p. 129).

Tal fato pode ser comprovado analisando a resposta em frequência da função transferência do compensador apresentado na Figura 30. O resultado é um ganho infinito para as frequências múltiplas da fundamental.

Figura 30 – Controlador Repetitivo. Fonte: Adaptado de Buso (2006, p. 130).

No entanto, pelos mesmos motivos, a sua estabilidade pode ser comprometida, uma vez que a amplificação infinita das componentes harmônicas de grandes ordens do sinal de erro pode reduzir a margem de fase da malha de controle. Para contornar tal problema, faz-se a adição dos filtros  $F_1(z)$  e  $F_2(z)$ , a fim de limitar a amplificação das harmônicas de altas frequências.

Para a implementação utilizou-se um proporcional em paralelo para melhorar as respostas transitórias, pois estas podem não ser satisfatórias devido a pequena margem de fase do controlador repetitivo. O controlador repetitivo escolhido para ser implementado, então, está apresentado na Figura 31.

Figura 31 – Controlador repetitivo com proporcional em paralelo. Fonte: Adaptado de Buso (2006, p. 132).

### **3 DESENVOLVIMENTO**

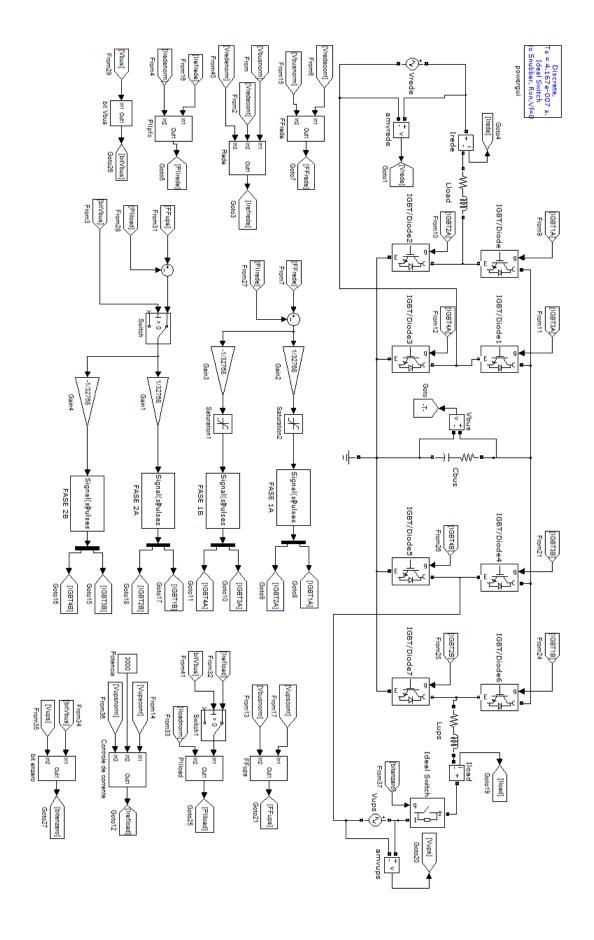

O desenvolvimento foi dividido em: simulação, dimensionamento e firmware.

## 3.1 SIMULAÇÃO

Para simular a carga eletrônica a ser desenvolvida neste trabalho, utilizou-se a ferramenta *Simulink* do programa *Matlab*. Para esta simulação, utilizamos a carga fixada em 3000 W, e para a carga não-linear, utilizamos uma forma de corrente de ponte retificadora com ângulo de condução do diodo de 45°.

Nesta seção estão apresentadas apenas partes do circuito simulado e o esquema completo da simulação pode ser visto no Apêndice A.

#### 3.1.1 Conversor da rede

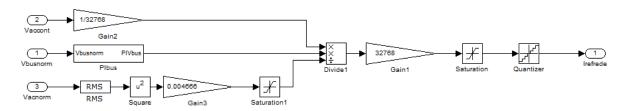

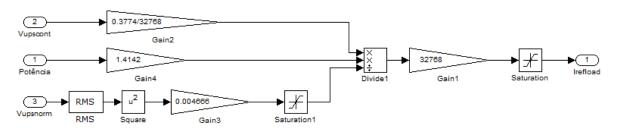

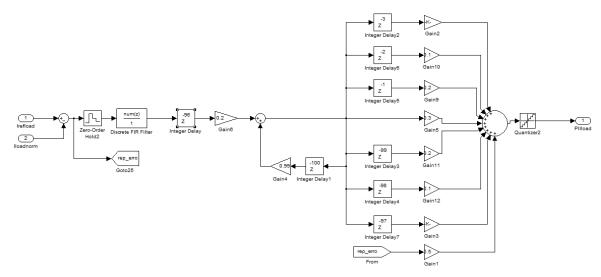

### 3.1.1.1 Geração da referência de corrente

O primeiro passo foi a implementação do conversor da rede, como na Figura 20, através da equação (12). A tensão regulada foi definida em 400 V, sendo esta referente ao barramento compartilhado. Esta tensão se mantém através desta equação, pois a saída do controlador PI do barramento retorna o valor da potência que está passando por ele. Sendo assim, quando a potência injetada no barramento aumenta, juntamente é aumentada a referência de corrente, evitando que a tensão do barramento suba, pois esta energia estará sendo devolvida à rede.

$$Iref_{rede} = \frac{Vrede_{cont}PI_{Vbus}}{Vrede_{RMS}^{2}0,004666}$$

(12)

Para que a simulação seja mais aproximada à implementação a ser feita no TCC, foram feitas normalizações em Q15 – onde 32768 pesos correspondem a 1 pu. Sendo assim, a normalização da variável  $Vac_{cont}$  foi fixada para um pico de 32768 pesos quando o pico da rede for 375 V, pois o fundo de escala da tensão de entrada da carga é de 265  $V_{RMS}$ . Igualmente, a variável  $Vrede_{RMS}^2$  foi normalizada pela constante 0,004666 para se ter 32768 pesos quando a tensão  $Vrede_{RMS}$  (normalizada em 10 pesos por volt) fosse 2650 pesos. O diagrama de blocos do Simulink pode ser visto na Figura 32.

Figura 32 – Diagrama do *Simulink* da geração de referência de corrente para a rede. Fonte: Os autores.

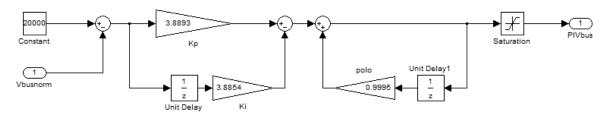

A partir da equação (13), controlador em atraso de fase da tensão do barramento foi implementado como na Figura 33, onde a amostra de tensão do barramento, *Vbus<sub>norm</sub>*, é normalizada em 50 pesos por volt. Os ganhos apresentados já estão com ajustes para que polo de malha fechada esteja dentro do círculo unitário e o zero esteja posicionado entre o polo e a origem, mantendo a estabilidade. O zero pode ser calculado a partir da equação (14).

$$u_{bus}[n] = 0.9995 \cdot u_{bus}[n-1] + 3.8893 \cdot e_{bus}[n] - 3.8854 \cdot e_{bus}[n-1]$$

(13)

$$zero_{bus} = \frac{K_i}{K_p} \tag{14}$$

$$zero_{bus} = \frac{3,8854}{3,8893} \tag{15}$$

Então,

$$zero_{bus} = 0,9990$$

Figura 33 – Diagrama do *Simulink* do atraso de fase da tensão do barramento. Fonte: Os autores.

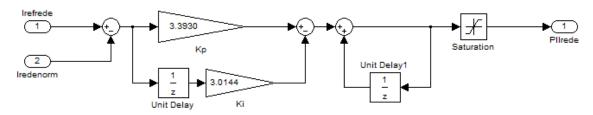

Como mencionado anteriormente, a saída do controlador do barramento retornará o valor da potência, fornecendo a amplitude da referência de corrente. A equação (16) apresenta a implementação do PI de corrente de entrada, e a Figura 34 a sua implementação no *Matlab*.

$$u_{\text{rede}}[n] = u_{\text{rede}}[n-1] + 3{,}3930 \cdot e_{\text{rede}}[n] - 3{,}0144 \cdot e_{\text{rede}}[n-1]$$

(16)

Figura 34 – Diagrama do *Simulink* do PI de corrente de entrada. Fonte: Os autores.

#### 3.1.1.2 Feed-forward

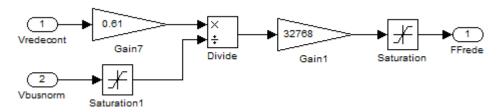

Para a geração do PWM dos IGBTs, é utilizado um *feed-forward* da tensão de entrada para diminuir o esforço realizado pelo PI. Neste *feed-forward* é realizado a realimentação negativa do PI de corrente da rede e é gerada a senóide a ser chaveada nos IGBTs. Tal *feed-forward* é implementado dividindo a variável *Vac<sub>cont</sub>* pela *Vbus<sub>norm</sub>* e multiplicando o resultado por 0,61 a fim de se ter um resultado de 1 pu de pico para quando a tensão de entrada for 265 V<sub>RMS</sub> e o barramento 400 V. O diagrama de blocos está apresentado na Figura 35.

Figura 35 – Diagrama do *Simulink* do *feed-forward*. Fonte: Os autores.

## 3.1.1.3 Geração do PWM

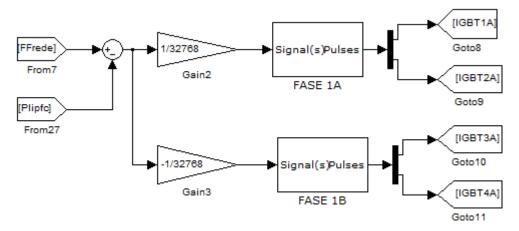

Por fim, gerou-se o PWM a ser chaveado nos IGBTs. O diagrama mostrando a implementação está na Figura 36.

Figura 36 – Diagrama do *Simulink* da geração de PWM. Fonte: Os autores.

A saída do demultiplexador retorna os PWMs defasados de 180° e a fase 1B é o PWM complementar que faz a comutação do segundo braço do inversor de entrada, como pode ser visto na Figura 37.

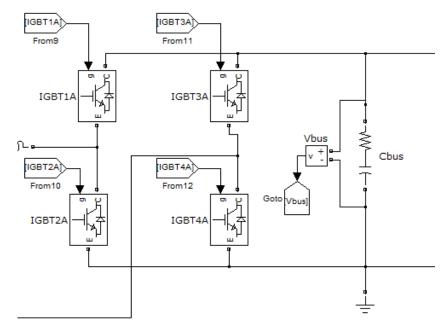

Figura 37 – Inversor de entrada. Fonte: Os autores.

### 3.1.2 Conversor do UPS

O problema da carga eletrônica também se resume na geração da referência de corrente e no controle desta. Para a geração da referência de corrente, utilizou-se a mesma equação do conversor da rede, apenas modificando as variáveis. Deste modo, podemos garantir um fator de potência unitário para simulações de cargas resistivas.

Para a simulação de cargas não-lineares, foi feito um diagrama lógico com correção do pico da corrente para se obter um fator de crista que se aproximasse da situação real.

### 3.1.2.1 Geração da referência de corrente

Como já mencionado, a forma com que a referência de corrente é semelhante à do conversor da rede. Esta está apresentada na equação (17).

$$Iref_{Load} = \frac{Vups_{cont} \cdot \sqrt{2} \cdot Potência}{Vups_{RMS}^2 \cdot 0,004666} \cdot 0,3774$$

(17)

A diferença entre as duas equações está na variável de potência no lugar do PI de tensão do barramento. A multiplicação por 0,3774 é para se obter uma normalização de corrente de 100 pesos por Ampére e a  $\sqrt{2}$  é para correção do fator de crista da senóide, visto que esta equação, sem a correção, retornaria o valor RMS da corrente em seu pico. A implementação no *Simulink* está apresentada na Figura 38.

Figura 38 – Diagrama do *Simulink* da geração de referência de corrente da carga. Fonte: Os autores.

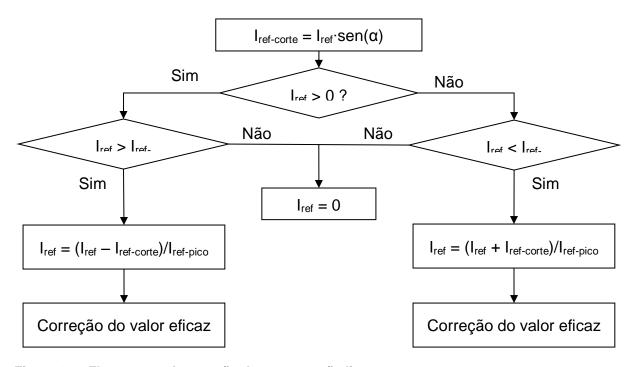

Figura 39 – Fluxograma da geração da corrente não linear Fonte: Os autores

A Figura 39 mostra o fluxograma para a geração da forma de onda nãolinear a ser utilizada neste trabalho. A lógica consiste em zerar a referência inferior à corrente de corte e subtrair o valor da corrente de corte para os valores superiores. O bloco seguinte à segunda verificação, tem como propósito manter o valor de pico para ambas as correntes (linear e não-linear). Após isto, ainda é adicionado um ganho para que o valor eficaz seja mantido para que a potência não seja diminuída.

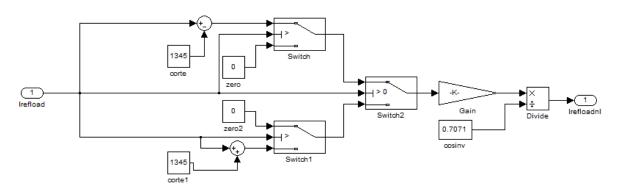

A lógica para a corrente não-linear implementada no Simulink está apresentada na Figura 40.

Figura 40 – Diagrama lógico do Simulink para geração da referência de corrente não-linear. Fonte: Os autores.

Na entrada tem-se a referência de corrente senoidal e em sua saída a referência de corrente não-linear. Relembrando que para o exemplo desta simulação, a potência foi fixada em 3000 W e o ângulo em 45°, o corte ficou em 13,45 A como pode ser visto nos blocos *corte* e *corte1* na Figura 40. Lembrando que este valor está em pesos, portanto para obter o valor em Ampéres, deve-se dividi-lo por 100.

#### 3.1.2.2 Controle de corrente

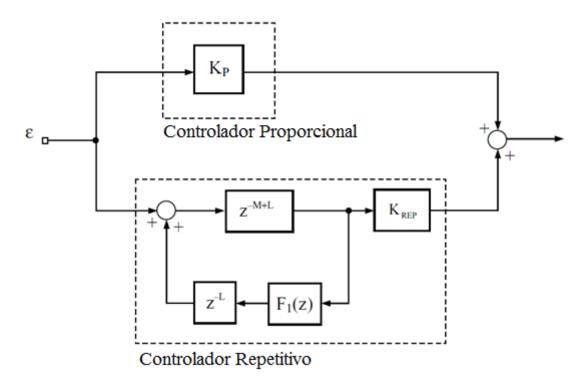

Devido às derivadas de corrente da carga não-linear, optou-se por utilizar o controle repetitivo para o controle de corrente.

A equação do controlador repetitivo fica como demonstrada na equação (18).

$$urp[n] = (urp[n-90] \cdot p_{rep}) + (e_{rep}[n-90 + Lag] \cdot G_{rep})$$

(18)

Devido à grande sensibilidade do controlador repetitivo, utilizou-se um filtro FIR (*Finite Impulse Response*) implementado por uma convolução de 8 pontos. Tal filtro funciona somando sua amostra atual mais as sete últimas multiplicadas por um ganho. No caso deste trabalho, o ganho utilizado nas oito amostras foi de 0,125.

O filtro de saída do controlador se assemelha ao de entrada, porém com sete amostras. As sete amostras são a atual [n], as 3 anteriores – [n-1] a [n-3] – e as 3 posteriores – [n+1] a [n+3]. As amostras posteriores são as amostras adiantadas em fase provenientes do ciclo anterior. Para o ganho das amostras com defasamento de três passos foi escolhido 0,05; para dois passos foi 0,1; para um passo foi 0,2; e para a atual foi 0,3.

Finalmente a implementação do controlador repetitivo fica como mostrado na equação (19)

$$urp[n-3] \cdot 0,05 + urp[n-2] \cdot 0,1 + urp[n-1] \cdot 0,2 + urp = urp[n] \cdot 0,3 + urp[n+1] \cdot 0,2 + urp[n+2] \cdot 0,1 + urp[n+3] \cdot 0,05$$

$$(19)$$

A fim de se obter uma resposta transitória mais suave, foi adicionado um controlador proporcional em paralelo com o controlador repetitivo.

A implementação do Simulink está demonstrada na Figura 41.

Na entrada, tem-se a referência de corrente linear ou não-linear sendo comparada com a corrente da carga eletrônica. O polo foi ajustado em 0,99, o ganho do repetitivo em 0,2, um atraso de 4 amostras e um ganho proporcional de 0,5 em paralelo.

Figura 41 – Diagrama do *Simulink* do controle repetitivo. Fonte: Os autores.

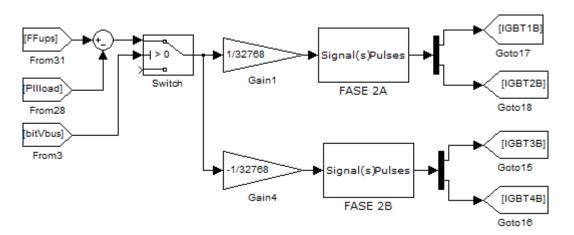

### 3.1.2.3 Geração do PWM

A geração do PWM é feita de forma semelhante à do conversor da rede, como demonstrado na Figura 42.

Figura 42 – Diagrama do *Simulink* da geração do PWM da carga eletrônica. Fonte: Os autores.

O *Feed-forward* é feito da mesma forma que o controle de corrente da rede. A chave existente na entrada foi adicionada para que o PWM só fosse gerado depois que o barramento estivesse estabilizado em 400 V.

IGBT3B

From21

IGBT3B

From24

IGBT3B

As respectivas chaves ficaram da forma mostrada na Figura 43.

Figura 43 – Inversor da carga eletrônica.

Fonte: Os autores.

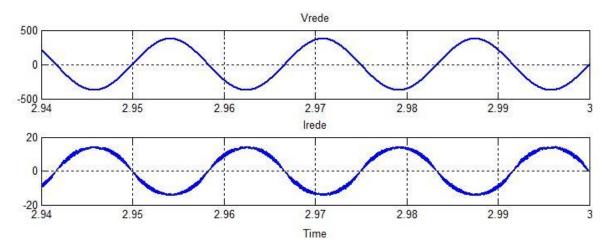

### 3.1.3 Resultados

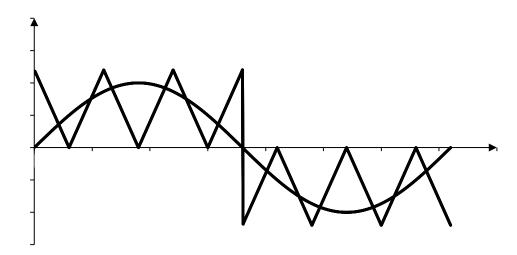

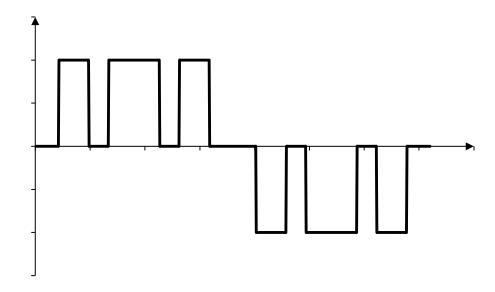

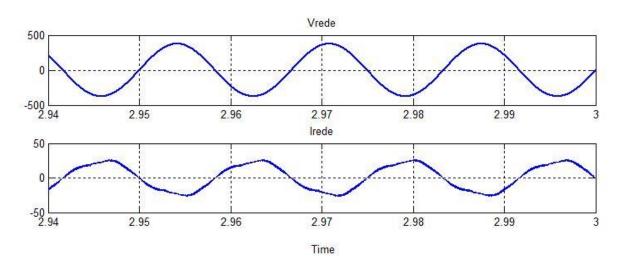

O resultado obtido para a carga linear está apresentado nas Figuras 44 e 45.

Figura 44 – Sinais resultantes da simulação de carga linear. Acima: tensão de entrada (Volts); abaixo: corrente de entrada (Amperes).

Fonte: Os autores.

Figura 45 - Referência de corrente (Pesos) e corrente da carga linear (Amperes) em regime permanente.

Fonte: Os autores.

Pode-se perceber na Figura 44, o bom funcionamento do controle de corrente da rede, uma vez que a corrente de entrada seguiu a tensão de entrada, mantendo uma forma de onda senoidal. Também, é interessante frisar que a corrente está 180° atrasada em relação à tensão, mostrando que, de fato, a energia absorvida pela carga está sendo regenerada para a rede.

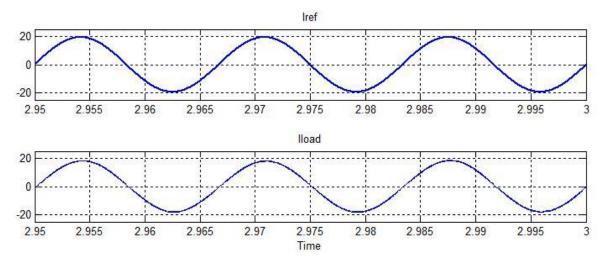

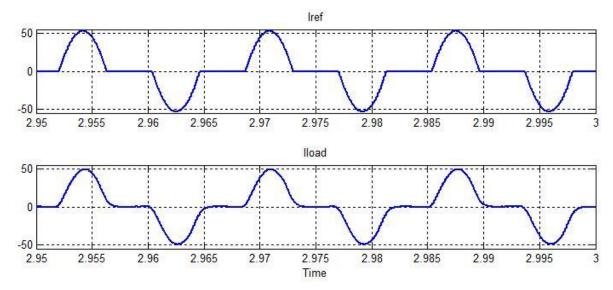

As Figuras 46 e 47 apresentam as aquisições dos mesmos sinais com a referência de corrente não-linear. Nesta, que estava a maior dificuldade, a corrente apresentou algumas componentes harmônicas.

Figura 46 - Sinais resultantes da simulação de carga não-linear. Acima: tensão de entrada (Volts); abaixo: corrente de entrada (Amperes).

Fonte: Os autores.

Figura 47 – Referência de corrente (Pesos) e corrente da carga não-linear (Amperes) em regime permanente.

Fonte: Os autores.

#### 3.1.4 Conclusão

O estudo realizado para a aquisição da revisão bibliográfica permitiu que os assuntos necessários para o entendimento e a simulação da carga eletrônica proposta fossem obtidos.

Definiu-se que o conversor utilizado seria o inversor ponte-completa, este tendo controles PI e repetitivo. Além disso, foram conhecidos os requisitos básicos de qualidade de energia para o funcionamento da carga eletrônica.

Com a simulação da carga eletrônica, foi possível perceber as dificuldades que se encontram ao se utilizar vários controladores, uma vez que todos devem estar trabalhando em sintonia para que o resultado desejado seja alcançado.

O controlador repetitivo teve um papel crucial, pois sem este não seria possível obter a forma de onda de carga não-linear devido às suas grandes derivadas.

As expectativas da simulação da carga eletrônica foram, portanto, atendidas, de forma que como próximo passo será realizada a implementação física da carga eletrônica proposta.

## 3.2 IMPLEMENTAÇÃO FÍSICA

Figura 48 – Placa montada da carga eletrônica. Fonte: Os autores.

Com a simulação feita, foi dado início à implementação do protótipo da carga eletrônica. Esta se deu em duas etapas: dimensionamento e desenvolvimento de firmware.

#### 3.2.1 Dimensionamento

Para iniciar a confecção da placa, foi necessário realizar o dimensionamento dos componentes como o capacitor do barramento, o indutor e capacitor de filtro e as chaves semicondutoras.

## 3.2.1.1 Capacitor do barramento

A troca de energia que ocorre no barramento ocasiona ondulações (*Ripple*) em sua tensão. Assim, o capacitor do barramento deve ser dimensionado de modo que o *Ripple* não ultrapasse a especificação do projeto.

Para este trabalho, foi especificado uma ondulação máxima de 10%, logo:

$$V_{bus} = 400 \, \text{V}$$

$$V_{bus-min} = 360 \text{ V}$$

Lembrando que:

$$f_{in} = 60\,\mathrm{Hz}$$

$$P = 5000 \, \text{W}$$

Utilizando a equação (20) (BARBI, 2006, p. 249) é possível chegar ao valor do capacitor que será necessário.

$$C = \frac{P}{2f_{in}(V_{bus}^2 - V_{bus-min}^2)}$$

(20)

$$C = \frac{5000}{2 \cdot 60 \cdot (400^2 - 360^2)} \tag{21}$$

Assim,

$$C = 1.37 \, \text{mF}$$

Para ter uma menor impedância resultante dos capacitores, utiliza-se vários em paralelo ao invés de um de valor elevado. Isto posto, utilizou-se quatro capacitores de 470 µF, resultando em uma capacitância equivalente de 1,88 mF.

### 3.2.1.2 Dimensionamento dos indutores

Para o dimensionamento dos indutores, foi usado a equação diferencial (22)

$$V = L \frac{di}{dt} \tag{22}$$

Isolando L,

$$L = V \frac{dt}{di} \tag{23}$$

Para a realização do cálculo, foi escolhida a pior situação com relação à derivada de corrente. Logo, a situação foi escolhida para o maior ângulo de disparo da corrente não-linear.

$$I = \frac{P}{V} = \frac{5000}{220} = 22,73 \,\text{A} \tag{24}$$

Considerando o fator de crista 3:1 (valor usual para cargas não-lineares), 68,18 A. Considerando que pode haver algumas ondulações na corrente, considerou-se uma corrente de pico de 70 A.

O intervalo de tempo considerado foi de 1,16 ms, equivalente à 25°. Tal ângulo se justifica, pois o ângulo máximo de disparo é 65°, logo a variação de ângulo até o pico é de 25°.

Voltando à equação (23) com os dados calculados:

$$L = (400 - 220\sqrt{2})\frac{1,16 \cdot 10^{-3}}{70} = 1,47 \,\text{mH}$$

(25)

Primeiramente, fez-se a escolha do condutor 10 AWG, pois sua capacidade de corrente é de 23,7 A (BARBI, p. 331, 2001). Apesar de esta escolha não ser a mais coerente se levado em consideração o efeito pelicular, a escolha foi mantida por se tratar de um produto e, obrigatoriamente, deve-se pensar em custos e mão de obra. Como a utilização desta bitola não afetará o funcionamento final da carga, optou-se pelo método menos custoso.

Para diminuir o volume do indutor, foi decidido utilizar 2 indutores – um em cada fase. Logo, a confecção do indutor foi feita calculando a metade da indutância para cada.

O dimensionamento do indutor foi feito a partir do *software* da empresa *Micrometals*. A escolha do número de núcleos foi feita de forma que as espiras coubessem em seu interior mantendo a indutância desejada.

| DC BIASED OUTPUT      | FILTER II | NDUCTOR  | ANALYSIS            |          |       |

|-----------------------|-----------|----------|---------------------|----------|-------|

| CORE PART NUMBER      |           | T225-34  | X 3 NUMBER IN STACK |          |       |

| WIRE GAGE             | 1         | # 10 AWG | X 1 STRANDS         |          |       |

| NUMBER OF TURNS       | ſ         | 85       |                     |          |       |

| DC BIAS CURRENT       |           | 0        | AMPERES             |          |       |

| PEAK INDUCTOR VOLTAGE | [         | 200      | VOLTS               |          |       |

| DC OUTPUT VOLTAGE     | [         | 200      | VOLTS               |          |       |

| FREQUENCY             | ſ         | 21.6     | k HERTZ             |          |       |

| AMBIENT TEMPERATURE   | Ī         | 25       | DEGREES C           |          |       |

|                       |           |          | <u>0</u> K          |          |       |

| INDUCTANCE            | 802 u     | Henry    | CORE LOSS           | 18.9     | W     |

| DC RESISTANCE         | 41.3 m    | OHMS     | COPPER LOSS         |          | W     |

| AC RESISTANCE         |           | OHMS     | BUILD               | 0.500    | in.   |

| RIPPLE CURRENT        |           | AMPS p-p | SURFACE AREA        | 177.1    | Sq cm |

| DC BIAS               |           | OES      | TEMP RISE @ 0 HRS   | 49.0     | DEG C |

| AC FLUX DENSITY       | 639       | GAUSS    | Time To 115 % Loss  | 2.39e+05 | Hours |

| PERCENT PERM          | 100       | PCT      | Life Limit          | 2.21e+06 | Hours |

| CORE AL VALUE         | 111       | nH       |                     |          |       |

Figura 49 – Dimensionamento do indutor a vazio

Fonte: Micrometals

O material foi escolhido de forma a balancear as perdas no cobre e no núcleo. Deste modo, o indutor não sofrerá grandes diferenças de aquecimento em operação ou em vazio.

| DC BIASED OUTPUT      | FILTER II | NDUCTOR  | ANALYSIS            |          |       |

|-----------------------|-----------|----------|---------------------|----------|-------|

| CORE PART NUMBER      | Ī         | T225-34  | X 3 NUMBER IN STACK |          |       |

| WIRE GAGE             | [         | # 10 AWG | X 1 STRANDS         |          |       |

| NUMBER OF TURNS       | ĺ         | 85       |                     |          |       |

| DC BIAS CURRENT       | ĺ         | 22.7     | AMPERES             |          |       |

| PEAK INDUCTOR VOLTAGE |           | 200      | VOLTS               |          |       |

| DC OUTPUT VOLTAGE     |           | 200      | VOLTS               |          |       |

| FREQUENCY             |           | 21.6     | k HERTZ             |          |       |

| AMBIENT TEMPERATURE   |           | 25       | DEGREES C           |          |       |

|                       |           |          | OK                  |          |       |

| INDUCTANCE            | 418 u     | Henry    | CORE LOSS           | 18.9     | W     |

| DC RESISTANCE         | 41.3 m    | OHMS     | COPPER LOSS         | 21.3     | W     |

| AC RESISTANCE         |           | OHMS     | BUILD               | 0.500    | in.   |

| RIPPLE CURRENT        | 11.07     | AMPS p-p | SURFACE AREA        | 177.1    | Sq cm |

| DC BIAS               | 166.1     | OES      | TEMP RISE @ 0 HRS   | 91.8     | DEG   |

| AC FLUX DENSITY       | 639       | GAUSS    | Time To 115 % Loss  | 4.59e+04 | Hours |

| PERCENT PERM          | 52        | PCT      | Life Limit          | 1.11e+05 | Hours |

| CORE AL VALUE         | 111       | nH       |                     |          |       |

Figura 50 - Dimensionamento do indutor com carga

Fonte: Micrometals

### 3.2.1.3 Dimensionamento do capacitor

O dimensionamento do capacitor foi feito após o dimensionamento do indutor utilizando a equação da frequência de corte (26).

$$\omega_C = \sqrt{\frac{1}{LC}} \tag{26}$$

$$2\pi f_{\rm C} = \sqrt{\frac{1}{LC}} \tag{27}$$

A frequência de corte deve ser, no mínimo, dez vezes menor que a frequência de chaveamento, logo 2,16 kHz.

$$2\pi 2,16\cdot 10^3 > \sqrt{\frac{1}{1,6\cdot 10^{-3}C}}$$

(28)

Logo,

$$C > 3.39 \mu F$$

Utilizou-se um capacitor de 5 µF, pois este é um valor comercial disponível e a frequência de corte fica definida em 1,8 kHz.

### 3.2.1.4 Dimensionamento das chaves semicondutoras

O tipo de chave semicondutora escolhida foi o IGBT (do inglês *Insulated Gate Bipolar Transistor*), devido à alta potência em que a carga irá trabalhar.

A escolha da chave se deu considerando os esforços aplicados a elas. Os esforços se resumem em:

$$V_{CF} = 200 \text{ V}$$

$$I_{M\acute{a}x} = 30 \, A$$

$$I_{Pico-M\acute{a}x} = 90 \,\mathrm{A}$$

Assim, fez-se a escolha do IGBT IRG4PSC71UD da *International Rectifiers*. Seus parâmetros são:

$$V_{CF} = 600 \, \text{V}$$

$$I_{M\acute{a}x} = 60 \, \text{A}$$

$$I_{Pico-M\acute{a}x} = 200 \,\mathrm{A}$$

$$V_{CE(on)} = 2 \text{ V}$$

$$V_{GE(th)} = 6 \text{ V}$$

$$i_{GE} = 100 \,\mathrm{nA}$$

#### 3.2.1.5 Acionamento das chaves semicondutoras

A etapa de potência da carga eletrônica deve estar isolada da parte lógica, para que os elementos desta não fiquem submetidos a grandes tensões e correntes.

Para o acionamento das chaves e isolação entre os comandos enviados pelo DSP às chaves foi utilizado um circuito *drive*.

O HCPL-316J é um *drive* optoacoplador que faz isolação entre entrada e saída, permitindo a esta correntes de até 150A e tensões de até 1200V.

O drive utilizado possui proteção para as chaves quando é detectada uma falta no circuito do IGBT. Quando a falta ocorre, a tensão no DESAT do HCPL atinge valores menores que 0,8V, levando o pino do FAULT ao nível alto e a corrente do IGBT ao valor nulo. O drive também possui um pino de RESET para que sofra interrupção por comando do DSP.

Para que não ocorra cruzamento entre as chaves comandadas através dos drives, é necessário um circuito de intertravamento na entrada nos HCPLs, fazendo com que a subida de uma das entradas não cruze com a descida da outra entrada.

Na saída do *drive*, foi utilizado um circuito que fornece tensão de 15V quando a saída possui sinal alto, para que os IGBTs escolhidos possam ser acionados. Quando a saída do *drive* possui sinal baixo, esta possui tensão de -12V, para que nenhum ruído seja percebido pelo IGBT como sinal de comando.

#### 3.2.1.6 Dimensionamento do transformador

O transformador de entrada tem como propósito apenas a isolação. Sendo assim, sua relação de transformação é de 1:1. Este foi dimensionado de modo a fornecer os 5 kVA que foram especificados para o projeto.

Para que se tenha o número de espiras desejado, é utilizada a equação (29) dada por Kosow (1982, p.520).

$$V_{TR} = 4,44 \cdot f \cdot A_{TR} \cdot n \cdot B_{TR} \tag{29}$$

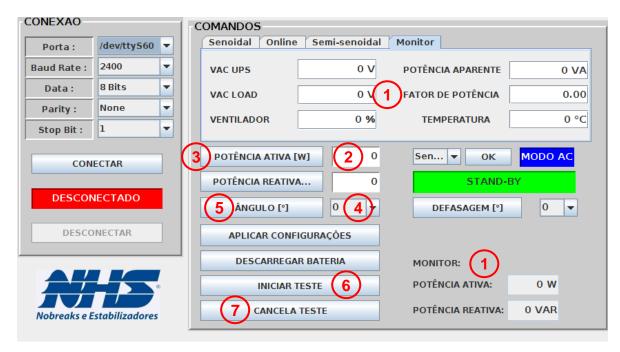

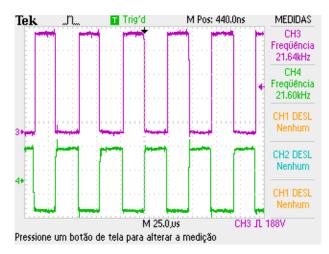

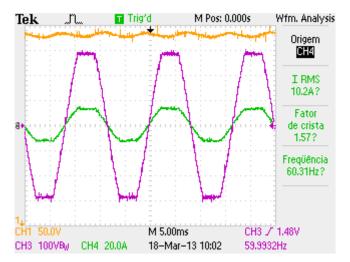

Onde  $V_{TR}$  é a tensão aplicada nos terminais do enrolamento, f é a frequência da tensão aplicada,  $A_{TR}$  é a área da perna central, n é o número de espiras e  $B_{TR}$  é o valor do fluxo magnético.