## UNIVERSIDADE TECNOLÓGICA FEDERAL DO PARANÁ PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA E INFORMÁTICA INDUSTRIAL

**EDUARDO PETERS**

COPROCESSADOR PARA ACELERAÇÃO DE APLICAÇÕES DESENVOLVIDAS UTILIZANDO PARADIGMA ORIENTADO A NOTIFICAÇÕES

DISSERTAÇÃO

## **EDUARDO PETERS**

# COPROCESSADOR PARA ACELERAÇÃO DE APLICAÇÕES DESENVOLVIDAS UTILIZANDO PARADIGMA ORIENTADO A NOTIFICAÇÕES

Dissertação apresentada ao Programa de Pós-Graduação em Engenharia Elétrica e Informática Industrial da Universidade Tecnológica Federal do Paraná, como requisito parcial para obtenção do grau de "Mestre em Ciências" — Área de Concentração: Engenharia de Automação e Sistemas.

Orientador: Prof. Dr. Volnei Antônio Pedroni Co-Orientador: Prof. Dr. Jean Marcelo Simão.

## Dados Internacionais de Catalogação na Publicação

#### P481

Coprocessador para aceleração de aplicações desenvolvidas utilizando paradigma orientado a notificações / Eduardo Peters. – 2012. 94 f. : il. ; 30 cm

Orientador: Volnei Antônio Pedroni.

Coorientador: Jean Marcelo Simão.

Dissertação (Mestrado) - Universidade Tecnológica Federal do Paraná. Programa de Pósgraduação em Engenharia Elétrica e Informática Industrial. Curitiba, 2012.

Bibliografia: f. 85-89.

1. Paradigma orientado a notificações. 2. Hardware. 3. Coprocessadores. 4. Software -Desenvolvimento. 5. Simulação (Computadores). 6. Engenharia elétrica – Dissertações. I. Pedroni, Volnei Antônio, orient. II. Simão, Jean Marcelo, coorient. III. Universidade Tecnológica Federal do Paraná. Programa de Pós-graduação em Engenharia Elétrica e Informática Industrial. IV. Título.

CDD (22. ed.) 621.3

# UNIVERSIDADE TECNOLÓGICA FEDERAL DO PARANÁ Câmpus Curitiba

Programa de Pós-Graduação em Engenharia Elétrica e Informática Industrial

## Título da Dissertação Nº 602

# "Coprocessador para Aceleração de Aplicações Desenvolvidas Utilizando Paradgima Orientado a Notificações"

por

# **Eduardo Peters**

Esta dissertação foi apresentada como requisito parcial à obtenção do grau de MESTRE EM CIÊNCIAS – Área de Concentração: Engenharia de Automação e Sistemas, pelo Programa de Pós-Graduação em Engenharia Elétrica e Informática Industrial – CPGEI – da Universidade Tecnológica Federal do Paraná – UTFPR – Câmpus Curitiba, às 9h30min do dia 31 de julho de 2012. O trabalho foi aprovado pela Banca Examinadora, composta pelos professores:

Prof. Volnei Antônio Pedroni , Dr. (Presidente – UTFPR)

Prof. Fabiano Silva, Dr. (UFPR)

Prof. Carlos Raimundo Brig Lima, Dr.

(UTFPR)

Visto da coordenação:

Prof. Ricardo Lüders, Dr. (Coordenador do CPGEI)

Aos meus pais Amauri e Elizabeth, que sempre me incentivaram e apoiaram em todas as fases de minha vida.

A minha noiva Mari Ane, que com carinho, compreensão e paciência ajudou-me a concretizar este sonho.

### **AGRADECIMENTOS**

Quero agradecer primeiramente a Deus, por tudo.

Agradeço a minha família, que me guiou durante toda a vida e sem a qual não teria chances de ter chegado até aqui.

Agradeço a minha noiva, Mari Ane Tromm, que me incentivou e apoiou durante toda a realização deste trabalho.

Ao meu orientador Volnei Antônio Pedroni, que com sabedoria e paciência me conduziu durante todo o período de mestrado. Pela sabedoria, direcionamentos e horas dispendidas na leitura de meus trabalhos.

Ao colega Ricardo Pereira Jasinski, a quem devo muito do meu conhecimento. Suas ideias e contribuições foram fundamentais para o desenvolvimento deste trabalho.

Ao Professor Jean Marcelo Simão, criador do Paradigma Orientado à Notificações, pelos direcionamentos e tempo dispendido na revisão de meus trabalhos.

Aos inventores do PON Professor Jean Marcelo Simão e Professor Paulo Cézar Stadzisz, bem como aos demais colaboradores da implementação em hardware do PON original, Robson Ribeiro Linhares, Fernando Augusto de Witt e Carlos Raimundo Erig Lima.

Agradeço aos colegas da Solvis, que pelas valiosas discussões contribuem grandemente ao meu aprendizado.

A todos os professores que passaram pela minha carreira acadêmica, pelo conhecimento repassado em suas aulas e UTFPR, pelas instalações e os materiais consumidos durante a realização desse trabalho.

Por fim, agradeço a todos os autores e todas as pessoas, que direta ou indiretamente contribuíram para a execução deste trabalho.

### RESUMO

Peters, Eduardo. Coprocessador para Aceleração de Aplicações Desenvolvidas Utilizando Paradigma Orientado a Notificações. 2012. 94 f. Dissertação - Programa de Pós-Graduação em Eng. Elétrica e Informática Industrial, Universidade Tecnológica Federal do Paraná. Curitiba, 2012.

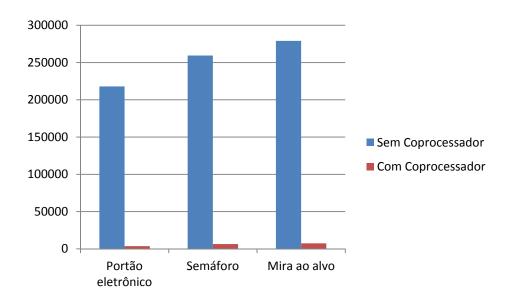

Este trabalho apresenta um novo hardware coprocessador para acelerar aplicações desenvolvidas utilizando-se o Paradigma Orientado a Notificações (PON), cuja essência se constitui em uma nova forma de influência causal baseada na colaboração pontual entre entidades granulares e notificantes. Uma aplicação PON apresenta as vantagens da programação baseada em eventos e da programação declarativa, possibilitando um desenvolvimento de alto nível, auxiliando o reuso de código e reduzindo o processamento desnecessário existente das aplicações desenvolvidas com os paradigmas atuais. Como uma aplicação PON é composta de uma cadeia de pequenas entidades computacionais, comunicando-se somente quando necessário, é um bom candidato a implementação direta em hardware. Para investigar este pressuposto, criou-se um coprocessador capaz de executar aplicações PON existentes. O coprocessador foi desenvolvido utilizando-se linguagem VHDL e testado em FPGAs, mostrando um decréscimo de 96% do número de ciclos de clock utilizados por um programa se comparado a implementação puramente em software da mesma aplicação, considerando uma dada materialização em um framework em PON.

Palavras chave: Paradigma Orientado a Notificações, *Hardware* coprocessador, Aceleração de *software*.

### **ABSTRACT**

Peters, Eduardo. Coprocessor for Accelerating Applications Developed with Notification Oriented Paradigm. 2012. 94 f. Dissertação - Programa de Pós-Graduação em Eng. Elétrica e Informática Industrial, Universidade Tecnológica Federal do Paraná. Curitiba, 2012.

This work presents a new hardware coprocessor to accelerate applications developed using the Notification-Oriented Paradigm (NOP). A NOP application has the advantages of both event-based programming and declarative programming, enabling higher level software development, improving code reuse, and reducing the number of unnecessary computations. Because a NOP application is composed of a network of small computational entities communicating only when needed, it is a good candidate for a direct hardware implementation. In order to investigate this assumption, a coprocessor that is able to run existing NOP applications was created. The coprocessor was developed in VHDL and tested in FPGAs, providing a decrease of 96% in the number of clock cycles compared to a purely software implementation.

Keywords: Notification Oriented Paradigm, Hardware coprocessor, software accelerating.

# **LISTA DE FIGURAS**

| Figura 1 - Comparação de vendas entre PCs e Sistemas Embarcados                       | 14   |

|---------------------------------------------------------------------------------------|------|

| Figura 2 - Preenchendo o espaço entre o processador e o ASIC                          | 16   |

| Figura 3 - Chips disponíveis para implementação de circuitos lógicos                  |      |

| Figura 4 - Relação entre as diferentes tecnologias de hardware                        | 21   |

| Figura 5 - Estrutura geral de uma FPGA                                                |      |

| Figura 6 - Estrutura de uma LUT de duas entradas                                      | 24   |

| Figura 7 - Flexibilidade dos dispositivos de hardware                                 | 25   |

| Figura 8 - Implementação conceitual do barramento Avalon                              | 31   |

| Figura 9 – Modelo simplificado de um coprocessador                                    |      |

| Figura 10 - Evolução das linguagens em relação aos paradigmas de programação          | o 37 |

| Figura 11 - Classificação dos atuais paradigmas                                       |      |

| Figura 12. Exemplo da cadeia de notificações dos componentes do PON                   | 41   |

| Figura 13 - Modelo Clássico de Desenvolvimento                                        |      |

| Figura 14 - Fluxo de desenvolvimento de sistemas baseados em HDLs                     |      |

| Figura 15 - Ambiente integrado de desenvolvimento para VHDL                           | 48   |

| Figura 16 - Ambiente integrado de desenvolvimento SBT                                 |      |

| Figura 17 - Representação dos componentes implementados no periférico                 |      |

| Figura 18 - Representação geral do sistema                                            |      |

| Figura 19 - Wizard para configuração do CoPON                                         |      |

| Figura 20 - Representação em <i>hardware</i> de um Atributo                           |      |

| Figura 21 - Representação em blocos da Premissa                                       |      |

| Figura 22 - Estrutura interna da Premissa                                             |      |

| Figura 23 - Representação do bloco de hardware da Condição                            |      |

| Figura 24 - Representação interna da Condição                                         |      |

| Figura 25 - Representação da FIFO de armazenamento das Regras aprovadas               |      |

| Figura 26 - Representação geral do periférico.                                        |      |

| Figura 27 – Hardware Acelerador                                                       |      |

| Figura 28 - Relação entre os objetos principais e colaboradores                       |      |

| Figura 29 – Código desenvolvido utilizando o framework PON original                   |      |

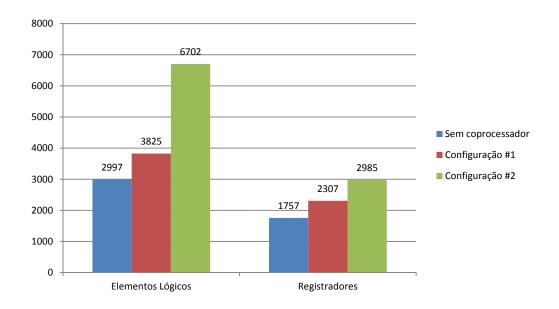

| Figura 31 – Acréscimo de <i>hardware</i> devido à adição do coprocessador             |      |

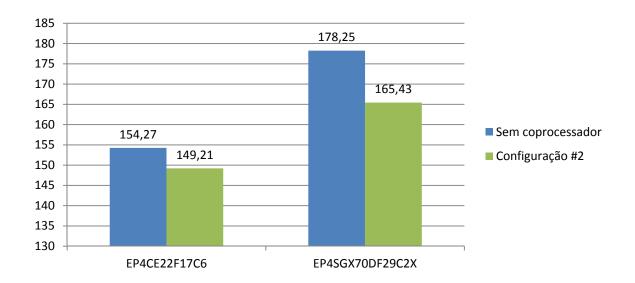

| Figura 32 - Frequência máxima de operação (f <sub>MAX</sub> )                         |      |

| Figura 33 - SoC criado para execução das aplicações                                   |      |

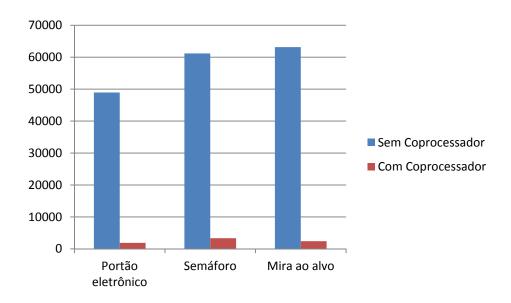

| Figura 34 – Número de ciclos de <i>clock</i> do momento da alteração de um Atributo a |      |

| a aprovação de uma Regra para execução                                                |      |

| Figura 35 – Número de ciclos de <i>clock</i> utilizados pelo sistema completo         | 82   |

# **LISTA DE TABELAS**

| Tabela 1 – Comparação entre número de ciclos de clock utilizados desde a alteração      |

|-----------------------------------------------------------------------------------------|

| de um Atributo até a aprovação de uma Regra para execução80                             |

| Tabela 2 – Comparação entre número de ciclos de <i>clock</i> utilizados pelo sistema em |

| aplicações com e sem hardware acelerador81                                              |

# LISTA DE QUADROS

| Quadro 1 - Mapa de memória de um Atributo PON                            | 57 |

|--------------------------------------------------------------------------|----|

| Quadro 2 - Mapa de memória de uma Premissa PON                           |    |

| Quadro 3 - Operações realizadas pela Premissa                            | 58 |

| Quadro 4 - Mapa de memória de uma Condição                               |    |

| Quadro 5 - Mapa de memória do periférico                                 | 66 |

| Quadro 6 - Configurações utilizadas para avaliação de custos de hardware |    |

## LISTA DE ABREVIATURAS E SIGLAS

A/D Analógico/Digital

ASIC Application-specific integrated circuit

CPLD Complex Programmable Logic Device

CPU Unidade central de processamento

ES Sistema Embarcado

FBE Elemento da base de fatos

FPGA Field Programmable Gate Array

HDL Linguagem de descrição de hardware

IEP Pipeline de execução de inteiros

IP Propriedade intelectual LISP Processamento de Listas

LU Unidade Lógica LUT Lookup Table

Opcode Código de operação

PC Contador de Programa

PF Paradigma Funcional

PL Paradigma Lógico

PLD Dispositivo lógico programável

PON Paradigma Orientado a Notificações

POO Programação Orientada a Objetos

PP Paradigma Procedimental

SBR Sistemas Baseados em Regras

SOC Sistema em um chip

SOPC Sistema em um chip programável

VHDL VHSIC hardware description language

# SUMÁRIO

| 1     | INTRODUÇÃO                                              | 13       |

|-------|---------------------------------------------------------|----------|

| 1.1   | APRESENTAÇÃO DO TEMA                                    | 13       |

| 1.2   | OBJETIVOS                                               | 17       |

| 1.3   | ESTRUTURA DA DISSERTAÇÃO                                | 18       |

| 2     | CONCEITOS E FUNDAMENTAÇÃO TEÓRICA                       | 19       |

| 2.1   | INTRODUCÃO                                              | 19       |

| 2.2   | INTRODUÇÃODISPOSITIVOS LÓGICOS PROGRAMÁVEIS             | 19       |

| 2.3   | CPU EM LÓGICA PROGRAMÁVEL                               |          |

| 2.4   | NIOS II                                                 |          |

| 2.4.1 | Barramento Avalon                                       |          |

| 2.4.2 | Interface Avalon MM                                     |          |

| 2.5   | COPROCESSADORES                                         |          |

| 2.6   | PARADIGMAS DE PROGRAMAÇÃO                               | 35       |

| 2.7   | PARADIGMA ORIENTADO A NOTIFICAÇÕES                      | 39       |

| 2.7.1 | Elementos da Base de Fatos                              |          |

| 2.7.2 | Atributos                                               |          |

|       | Premissas                                               |          |

| 2.7.4 | Condições                                               |          |

| 2.7.5 | Regras                                                  |          |

| 2.7.6 | Ações                                                   |          |

| 2.7.7 | Instigações                                             |          |

| 2.7.8 | Métodos                                                 |          |

| 2.8   | REFLEXÃO                                                |          |

| 3     | DESENVOLVIMENTO                                         |          |

| 3.1   | INTRODUÇÃO                                              |          |

| 3.2   | DESENVOLVIMENTO DO HARDWARE EM HDL                      |          |

| 3.2.1 | Especificação e Desenho                                 |          |

| 3.2.2 | Micro Desenho                                           |          |

| 3.2.3 | Codificação em Nível de Transferência de Registro – RTL |          |

| 3.2.4 | Simulação e Testes                                      |          |

| 3.2.5 | Síntese, Alocação e Roteamento                          | 43<br>49 |

| 3.3   | DESENVOLVIMENTO DE SOFTWARE                             |          |

| 3.4   | ESTRUTURA DO PON EM <i>HARDWARE</i>                     |          |

| _     |                                                         |          |

|       | Premissas                                               |          |

|       | Condição                                                |          |

| 3.4.4 | Regra                                                   |          |

| 3.4.5 | Interface e Lógica de Configuração                      | 62<br>63 |

| 3.4.6 | Interface com o NIOS II                                 |          |

| 3.4.7 |                                                         |          |

| 3.5   | ALTERAÇÕES NO FRAMEWORK                                 | 67       |

| 3.6   | FLUXO DE EXECUÇÃO DO COPROCESSADOR                      | 70       |

| 3.7   | REFLEXÃO                                                | 73       |

| 4     | RESULTADOS                                              |          |

| 4.1   | INTRODUÇÃO                                              |          |

|       | Comparações de Utilização de Recursos de Hardware       |          |

|       | Comparações de Desempenho de Aplicação                  |          |

| 5     | CONSIDERAÇÕES FINAIS E TRABALHOS FUTUROS                | 83       |

| 5.1         | TRABALHOS FUTUROS | 84 |

|-------------|-------------------|----|

| REFEI       | RÊNCIAS           | 85 |

| <b>APÊN</b> | DICES             | 90 |

## 1 INTRODUÇÃO

## 1.1 APRESENTAÇÃO DO TEMA

Grande parte dos sistemas computacionais atuais consiste em sistemas embarcados, os quais são sistemas computacionais especializados em desempenhar funções específicas.

Segundo Wolf (2002, p.136), "um Sistema Embarcado (ES) é qualquer computador que seja um componente de um sistema maior e que possui processamento próprio". Por serem projetados para executar uma ou algumas poucas funcionalidades específicas, os sistemas embarcados utilizam a menor quantidade possível de *hardware* para desenvolver suas tarefas, garantindo assim um custo reduzido, menor consumo de energia e devido à sua especialização, maior eficiência.

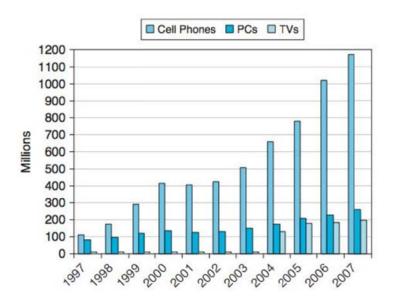

No mundo atual o número de dispositivos embarcados é muito superior ao número de computadores de uso pessoal, como pode-se observar na Figura 1. Esta comparação é feita somente utilizando um tipo específico de sistema embarcado, os telefone celulares. Entretanto este número pode ser facilmente multiplicado se considerarmos outros tipos de sistemas embarcados, como eletrodomésticos, players multimídia, equipamentos para automação, eletrônica automotiva etc.

Em contrapartida, por se tratar de um sistema com recursos reduzidos, existem grandes limitações de processamento, consumo de memória e consumo de energia, tornando complexo o desenvolvimento de software para estes sistemas.

Neste âmbito, os atuais paradigmas de programação, com suas respectivas linguagens e *frameworks*, não contribuem para a construção de programas eficientes. Nestes, as expressões causais (e.g. comandos se-então) e os dados (e.g. variáveis) são tratados como entidades passivas, as quais são relacionadas por meio de pesquisa estabelecida pelo fluxo de execução dos programas. Isto causa inclusive um considerável desperdício de processamento (BANASZEWSKI, 2009).

Figura 1 - Comparação de vendas entre PCs e Sistemas Embarcados

Fonte: Patterson e Hannessy (2011)

O Paradigma Orientado a Notificações (PON)<sup>1</sup> é uma alternativa aos atuais paradigmas de programação (SIMÃO;STADZISZ, 2008) (BANASZEWSKI, 2009). Como neste paradigma as relações causais possuem uma conotação reativa, onde cada entidade que tem seu valor alterado tem a função de notificar as alterações às entidades afetadas pela sua mudança, há inclusive um menor desperdício de processamento.

Ademais, a programação em PON se torna mais fácil, por possuir um estilo de programação próximo à forma cognitiva humana, permitindo a representação do conhecimento de maneira natural ao ser humano, na forma de regras, visando alcançar esforços mínimos na programação em termos de escrita de código (BANASZEWSKI, 2009).

industrial com subsequente pedido de patente (SIMÃO et al, 2012c). Assim sendo, a utilização do PON se submete ao respeito dos direitos relativos a esta potencial patente.

-

<sup>&</sup>lt;sup>1</sup> Salienta-se que o PON é atualmente objeto de pedido de patente junto ao INPI (Instituto Nacional de Propriedade Industrial) sob Número Provisório 015080004262 e número efetivo PI0805518-1, via Agência de Inovação da UTFPR (SIMÃO; STADZISZ, 2008). Há ademais outros pedidos de patente relativos ao PON (SIMÃO; STADZISZ, 2009b) (SIMÃO et al, 2010). Há ainda um pedido de proteção

Por outro lado, por estar o PON materializado ainda sob a forma de um framework<sup>2</sup> para a linguagem de programação C++, o PON utiliza elevados recursos de hardware, com grande uso de memória de trabalho e processamento, dificultando assim seu uso em sistemas embarcados (LINHARES, 2011)(VALENÇA, 2011).

O desenvolvimento de sistemas totalmente customizados de acordo com a aplicação tem possibilitado desenvolver produtos de alta tecnologia com baixo custo e consumo reduzido de energia. Para isso, é necessário aperfeiçoar a lógica e o processador do sistema embarcado de acordo com a sua função. O consumo de energia também é reduzido devido a esta otimização, pois o processador pode operar em uma menor frequência, já que possui alto desempenho.

Uma das possibilidades para criação de sistemas embarcados, é a implementação de sistemas embarcados completos em lógica programável, contendo processador, periféricos de entrada e saída e *hardware* customizado à aplicação. Com a crescente evolução tecnológica dos dispositivos de lógica programável (e.g. FPGAs), disponibilizando uma grande quantia de unidades lógicas em um único circuito integrado, torna-se possível criar dispositivos altamente complexos em um único *chip*.

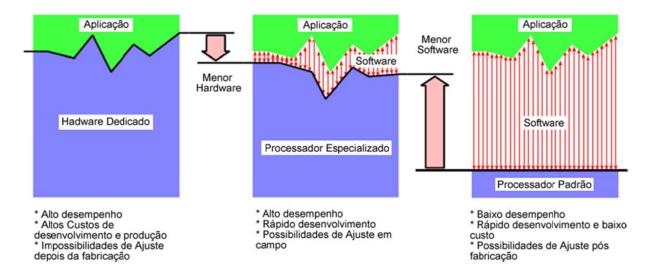

Neste âmbito, as implementações com *software* permitem maior flexibilidade que as realizadas em *hardware*, porém as implementações em *hardware* permitem obter maior desempenho. Assim, fica a cargo do projetista optar por uma ou outra, ou ainda um misto das duas, de acordo com os requisitos do sistema.

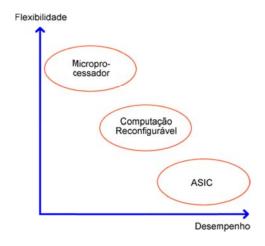

De fato, uma alternativa para a implementação de sistemas embarcados é o uso da computação reconfigurável (COMPTON; HAUCK, 2002, p.172). A Figura 2 apresenta um gráfico comparativo, relacionando o desempenho e flexibilidade das FPGAs em relação ao ASIC e aos microprocessadores de propósito geral.

Além disso, existem algumas evidências mostrando que o número de transistores por FPGA está crescendo mais do que em microprocessadores, sendo comparado com a curva de crescimento da tecnologia de memória, indicando que

<sup>&</sup>lt;sup>2</sup> A versão do *framework* utilizada no desenvolvimento deste trabalho foi proposta por (BANASZEWSKI, 2009). Salienta-se que este *framework* está em constante desenvolvimento e já existe uma nova versão com melhorias no desempenho e utilização de recursos.

em um futuro próximo poderão existir FPGAs com desempenho semelhante aos encontrados hoje nos processadores.

O uso da computação reconfigurável possibilita constante melhoria do hardware dos sistemas computacionais, uma vez que o hardware é descrito através de uma linguagem de descrição de hardware (HDL), sem que sejam necessárias alterações físicas de hardware, resultando em sistemas eficientes, compactos, de baixo consumo de energia e de custo reduzido.

Figura 2 - Preenchendo o espaço entre o processador e o ASIC

Fonte: adaptado de HARTENSTEIN (2001, p. 642)

A computação reconfigurável objetiva preencher a lacuna entre *hardware* e *software*, alcançando um desempenho muito maior que o *software*, e mantendo um grau de flexibilidade muito maior que o *hardware* (COMPTOM; HAUCK, 2000, p.171). Uma das abordagens para o uso da computação reconfigurável pode se dar através do uso de microprocessadores de uso geral, juntamente com *hardware* customizado. Dessa forma pode se obter o benefício de se desenvolver *software* com ferramentas padronizadas e obter um desempenho ótimo de partes específicas do *software*.

Um coprocessador é um conjunto especial de circuitos, desenvolvido para executar tarefas específicas mais rapidamente que um circuito microprocessador básico poderia fazer para executar a mesma tarefa. Um coprocessador é responsável por tarefas de processamento especializado, permitindo que o

processador seja liberado dessas tarefas, enquanto o processamento pesado e específico fica a cargo do coprocessador.

Nesse contexto surge a oportunidade de criar uma solução de sistema embarcado em uma FPGA, contendo um processador customizado com um periférico capaz de acelerar aplicativos desenvolvidos seguindo o Paradigma Orientado a Notificações, tornando-o uma alternativa possivelmente viável para o uso em sistemas embarcados dessa natureza.

### 1.2 OBJETIVOS

Como uma aplicação PON é composta de uma cadeia de pequenas entidades computacionais inteligentes, comunicando-se somente quando necessário, torna-se um bom candidato à implementação em *hardware*. Para investigar este pressuposto, o objetivo principal dessa dissertação é estudar e discutir a construção um *hardware* periférico, capaz de acelerar a execução de *softwares* criados seguindo o Paradigma Orientado a Notificações, tornando dessa forma, viável o uso pleno do PON em sistemas embarcados construídos utilizando-se processadores genéricos.

Serão apresentadas descrições de cada componente da cadeia de notificações e sua implementação correspondente em *hardware*, bem como a integração dos componentes em um sistema, passível de uso em processadores comerciais.

Para isso, foram definidos os objetivos específicos listados a seguir:

- Analisar o PON através da bibliografia, conceitos e aplicações existentes e definir quais componentes podem efetivamente trazer resultados satisfatórios se implementados em hardware

- Modelar o sistema de aceleração a partir da implementação existente em software

- Criar e testar o hardware proposto para aceleração do PON

- Integrar o hardware de aceleração do PON a um processador comercial existente

- Realizar as alterações no framework atual, para que o mesmo utilize o novo acelerador

- Realizar estudos de caso, a fim de avaliar os ganhos e impactos causados pela adição do novo componente.

# 1.3 ESTRUTURA DA DISSERTAÇÃO

Para apresentar as tecnologias necessárias e demonstrar o desenvolvimento e comparações da implementação de um periférico acelerador do PON, esta dissertação está organizada em cinco capítulos.

O primeiro capítulo introduz o tema desta dissertação ao leitor.

O segundo capítulo traz uma breve revisão da literatura pertinente ao trabalho, apresentando os conceitos necessários ao entendimento dos sistemas embarcados, a tecnologia dos dispositivos lógicos programáveis, utilizada para implementação do periférico para o processador NIOS II e a teoria envolvida na criação do paradigma orientado a notificações.

O terceiro capítulo apresenta o desenvolvimento propriamente dito do periférico acelerador, ou seja, toda a especificação e maneira como estruturou-se periférico.

No quarto capítulo apresenta-se uma comparação de desempenho entre aplicações desenvolvidas utilizando o periférico acelerador do PON e as mesmas aplicações utilizando o PON em sua forma tradicional, ambos executados no processador Altera NIOS II, sintetizado em uma FPGA.

No quinto capítulo são discutidos os resultados e apresentadas as conclusões do trabalho e trabalhos futuros.

# 2 CONCEITOS E FUNDAMENTAÇÃO TEÓRICA

## 2.1 INTRODUÇÃO

Com a crescente evolução tecnológica das FPGAs, disponibilizando uma grande quantia de unidades lógicas (LU) em um único circuito integrado, torna-se possível implementar dispositivos altamente complexos em um único *chip*. Uma das possibilidades é a implementação de sistemas microprocessados completos em lógica programável.

Outrossim, com a atual complexidade no desenvolvimento dos mesmos, aspira-se por uma maneira mais eficaz e natural de construir softwares para este tipo de sistema computacional.

O Paradigma Orientado a Notificações surge como uma alternativa aos paradigmas atuais de desenvolvimento, utilizados para a criação de sistemas embarcados, mas enfrenta problemas quanto ao uso de recursos como memória e processamento em sistemas dessa natureza.

Apresenta-se nesse capítulo a fundamentação teórica necessária ao entendimento do desenvolvimento de um sistema coprocessador, que visa tornar a utilização do PON viável em sistemas embarcados.

## 2.2 DISPOSITIVOS LÓGICOS PROGRAMÁVEIS

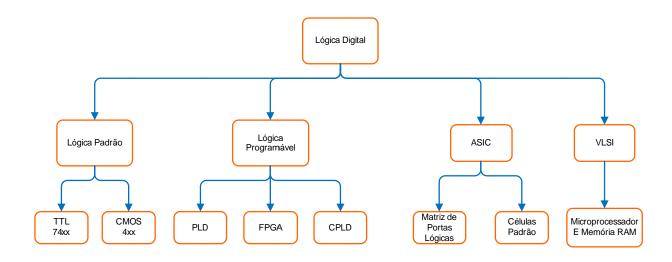

Além dos computadores em si, também a maneira como os sistemas digitais são elaborados tem evoluído drasticamente nas últimas décadas. Até a década de 60, os sistemas digitais eram construídos a partir de componentes discretos, tais como transistores e resistores. Com o surgimento de circuitos integrados (*chips*), foi possível integrar muitos transistores dentro de uma única pastilha de silício, dando subsídios à criação de uma vasta gama de produtos.

Tradicionalmente, os *chips* realizam operações pré-definidas pelo fabricante. Assim, para a elaboração de um circuito com lógica definida pelo usuário, há necessidade do uso de tipos diferentes de *chips*. Isto implica em diversas desvantagens ao sistema, como aumento da área necessária para a conexão, perda de desempenho devido ao atraso existente nas portas de entrada/saída e aumento do consumo de energia.

Para contornar estes problemas, surgiram outros tipos de circuitos integrados, os quais possuem as funcionalidades definidas não mais pelo fabricante, mas sim pelo usuário. Dentre estes, encontram-se os Circuitos Integrados de Aplicação Específica (ASIC), Dispositivos Lógicos Programáveis (PLD), Dispositivos Lógicos Programáveis Complexos (CPLD), *Field-Programmable Gate Array* (FPGA), Matriz Lógica Programável (PLA) etc.

Esta evolução permitiu que uma grande variedade de *chips* baseada em sistemas transistorizados fosse construída nestas pastilhas de silício, as quais são apresentadas na Figura 3.

A funcionalidade existente em um chip do tipo ASIC é definida pelo usuário, mas implementada pelo fabricante devido à tecnologia necessária para este processo, a qual possui um custo elevado. Esta funcionalidade é fixa, ou seja, após o *chip* ter sido fabricado não é possível realizar atualizações em suas funções de *hardware*. Apesar desta desvantagem, este tipo de circuito integrado geralmente tem baixo consumo de energia, seu desempenho é alto devido à sua especificidade e o custo do sistema tende a reduzir-se quando produzido em larga escala.

Figura 3 - Chips disponíveis para implementação de circuitos lógicos

Fonte: (adaptado de HAMBLEN; FURMAN, 2001, p.38)

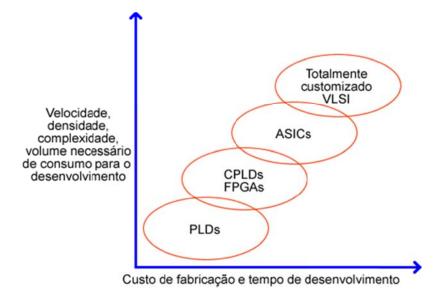

Já os PLDs, FPGA e CPLDs permitem ao próprio usuário definir e implementar em campo a funcionalidade do chip. Deste modo, o custo de desenvolvimento e o tempo necessário para a obtenção do produto são inferiores aos de um ASIC. Porém, há um pior desempenho e um aumento de densidade e complexidade do chip (HAMBLEN; FURMAN, 2001, p.39). Através da Figura 4, pode-se observar a relação entre as tecnologias mencionadas anteriormente.

Figura 4 - Relação entre as diferentes tecnologias de hardware

Fonte: (adaptado de HAMBLEN; FURMAN, 2001, p.39)

Dispositivos lógicos programáveis (PLD) são dispositivos configuráveis após a fabricação, utilizados para construir circuitos lógicos. Ao contrário de um ASIC, que tem uma função fixa após a fabricação, um PLD tem uma função indefinida quando fabricada e antes de sua utilização este deve ser programado, para que suas funções sejam estabelecidas.

Os PLDs foram introduzidos nos anos 70 e são *chips* de propósito geral que podem ser utilizado para implementar quaisquer tipos de circuitos lógicos (BROWN; VRANESIC, 2005, p.94). Dentro do chip há uma coleção de elementos lógicos fundamentais, que podem ser interligados e configurados de diferentes maneiras.

O PLD pode ser visto como um circuito sem funcionalidade definida, que contém portas lógicas e chaves (*switches*) programáveis. As chaves programáveis permitem conectar as portas lógicas internas ao PLD para implementar quase todos os tipos de circuitos lógicos existentes, definindo assim a sua funcionalidade.

Uma FPGA (*Field Programmable Gate Array*) é um dispositivo que não implementa a função lógica no método tradicional; nela, cada elemento lógico individual é na verdade uma pequena matriz de memória, programada diretamente com a função desejada a partir de uma tabela verdade (BERGER, 2002, p.177).

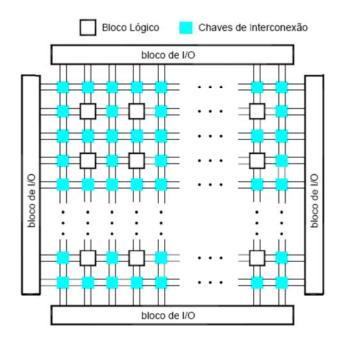

A estrutura geral de uma FPGA é apresentada na Figura 5, apresentando três tipos de recursos: blocos de I/O para conectar os pinos de entrada e saída do dispositivo, blocos lógicos dispostos num arranjo bidimensional e um conjunto de chaves de interconexão organizadas como canais de roteamento horizontal e vertical entre as linhas e colunas dos blocos lógicos.

Figura 5 - Estrutura geral de uma FPGA

Fonte: (BROWN; VRANESIC, 2005, p.106)

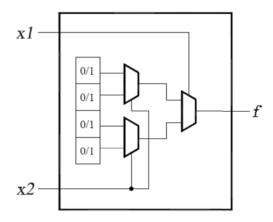

Os canais de conexão entre os blocos lógicos são constituídos por condutores internos e pelas chaves existentes na FPGA. Cada bloco lógico em um FPGA tipicamente possui um pequeno número de entradas e uma saída. Os mais comuns são os baseados em *Lookup Tables* (LUTs), que contêm células de armazenamento usadas para implementar uma pequena função lógica. LUTs de vários tamanhos podem ser criadas, onde o tamanho é definido pelo número de entradas. A Figura 6 apresenta a estrutura de uma pequena LUT com duas entradas (x1 e x2) e uma saída (f), a qual é capaz de implementar qualquer função de duas variáveis. Devido à tabela verdade de duas variáveis possuir quatro combinações possíveis, esta LUT possui quatro células de armazenamento. As variáveis de entrada x1 e x2 são usadas como seletores de entrada dos três multiplexadores, que dependendo dos valores de x1 e x2 selecionam o conteúdo de uma das quatro células como saída da LUT. As FPGA disponíveis no mercado geralmente possuem LUTs de quatro a oito entradas.

Quando um circuito lógico é implementado em um FPGA, os blocos lógicos são programados para realizarem as funções necessárias e as chaves de interconexão são programadas para definir o canal de comunicação entre estes

blocos lógicos. As células de armazenamento nas LUTs em uma FPGA são voláteis; deste modo, todas as vezes que o dispositivo for energizado deverá ter suas LUTs programadas. Frequentemente, uma PROM (*Programmable Read-Only Memory*) ou uma EPROM (*Erasable Programmable Read-Only Memory*) é incluída no circuito da placa onde se encontra a FPGA, com a finalidade de automaticamente carregar a configuração da FPGA quando o chip é energizado, através de um *hardware* específico para esta função.

Figura 6 - Estrutura de uma LUT de duas entradas

Fonte: (BROWN; VRANESIC, 2005, p.107)

Atualmente existem diversos fabricantes de dispositivos FPGA, dentre os quais podemos citar as empresas Altera, Xilinx, Actel, Cypress Semiconductor, QuickLogic e Lattice/Vantis Corporation. As empresas Altera Corp. e Xilinx Inc. possuem a maior fatia deste mercado, oferecendo uma grande variedade de dispositivos de alto desempenho, alta densidade e relativamente baixo custo.

O uso de *hardware* reconfigurável possibilita que o circuito integrado seja configurado em campo de acordo com a aplicação, além de permitir atualizações do *hardware* já criado. Esta flexibilidade permite obter sistemas de alto desempenho, otimizados de acordo com a aplicação e com tempo de desenvolvimento baixo se comparado aos sistemas discretos e aos implementados em ASIC.

A computação reconfigurável objetiva preencher a lacuna entre *hardware* e *software*, alcançando um desempenho muito maior que o *software* e mantendo um grau de flexibilidade muito maior que o *hardware* (COMPTOM; HAUCK, 2000,

p.171). A Figura 7 apresenta a relação entre a aplicação e o dispositivo de *hardware* existente nas três alternativas descritas anteriormente, demonstrando algumas das vantagens e desvantagens de cada tipo de implementação.

Como a computação reconfigurável está baseada nas linguagens de descrição de *hardware* (HDLs) é possível que o *hardware* seja descrito através de arquivos-fonte. Desta forma, modificando somente tais arquivos há a possibilidade de se atualizar todo o *hardware* do sistema. Esta atualização pode ser feita tanto na inicialização do dispositivo como em tempo de execução.

Figura 7 - Flexibilidade dos dispositivos de hardware

Fonte: adaptado de Ienne, Pozzi e Vuletic (2002, p.2)

Tecnologias mais recentes de FPGAs permitem uma operação denominada reconfiguração dinâmica ou em tempo de execução. Esta operação é caracterizada pela habilidade de substituição de contextos de *hardware* ou subsistemas digitais para rapidamente modificar (durante a operação) as funcionalidades dos componentes em operação e as suas interconexões (ESKINAZI *et al*, 2005). Esta abordagem permite que um novo *hardware* possa ser criado para suprir uma deficiência de *software* durante a execução do programa.

## 2.3 CPU EM LÓGICA PROGRAMÁVEL

Nos últimos anos, os sistemas embarcados, também conhecidos como computação embarcada vêm se tornando um novo modelo para o projeto e implementação de dispositivos eletroeletrônicos modernos, tais como câmeras filmadoras, telefones celulares, dispositivos de controle automotivos e equipamentos médicos, dentre outros. Estes dispositivos possuem processadores que podem alcançar níveis de desempenho em sua tarefa específica semelhantes ao de um poderoso computador, o que certamente não seria alcançado com o uso de um simples microprocessador de propósito geral.

Com a crescente evolução tecnológica das FPGAs, disponibilizando uma grande quantia de unidades lógicas (LU) em um único circuito integrado, torna-se possível implementar dispositivos altamente complexos em um único *chip*. Uma das possibilidades é a implementação de sistemas microprocessados completos em lógica programável.

A CPU é o centro de todo sistema computacional, seja ele um sistema de processamento genérico, um sistema embarcado, microcontrolador ou qualquer outro. O trabalho da CPU é executar rigorosamente as instruções de um programa, na sequência definida, para uma aplicação específica. As operações elementares realizadas por uma CPU são: leitura de informações de entrada, leitura da memória de trabalho, transformações sobre os dados nela armazenados e escrita de informações na memória e periféricos. Um programa computacional (software) é composto por uma sequência destas operações básicas, e é responsável por garantir que a CPU realize as tarefas desejadas.

As ações de um processador de uma forma geral se resumem às ações buscar instruções na memória, decodificá-las e executá-las<sup>3</sup>, sendo processadas repetidamente:

Buscar a instrução apontada pelo contador de programa (PC<sup>4</sup>) da memória e carregá-la no registrador de instrução.

\_

<sup>&</sup>lt;sup>3</sup> Do Inglês *Fetch, Decode* e *Execute,* geralmente encontrados na literatura.

- 2. Mudar o PC, apontando-o para a próxima instrução da memória.

- 3. Decodificar a instrução, determinando o seu tipo, operandos etc.

- Se a instrução usa operandos (dados) da memória, determinar os seus endereços.

- 5. Buscar os dados de memória e carregá-los nos registradores.

- 6. Executar a instrução.

- 7. Armazenar resultados (em registradores ou memória).

Os programas usam códigos para fornecer instruções para a CPU. Estes códigos são chamados de *códigos de* operação, ou *opcodes*<sup>5</sup>. Cada *opcode* instrui a CPU a executar uma sequência específica de ações.

A implementação de CPUs ou de sistemas microprocessados em dispositivos programáveis, além de apresentar todas as vantagens inerentes à reconfigurabilidade, traz uma série de benefícios em relação ao emprego de CPUs convencionais (JASINSKI, 2004, p.2). Notam-se esses benefícios a partir do aumento de desempenho do sistema com a implementação de rotinas diretamente em *hardware* ao invés da tradicional implementação via *software*.

A CPU Nios II 6.0, por exemplo, permite que a instrução de multiplicação seja realizada através de rotinas de *hardware*, proporcionando um ganho de até 80 ciclos de *clock* se comparado à execução por *software* (*Altera*, 2012b).

Modelos mais recentes de CPUs, criados especificamente para a implementação em lógica programável, são facilmente adaptáveis a aplicações específicas. Além da possibilidade de se acrescentar novas instruções, outras já existentes podem ser configuradas para executarem mais rapidamente ou utilizarem menos recursos de *hardware* (computação espacial × temporal) (JASINSKI, 2004, p.5).

Hoje em dia podemos encontrar no mercado alguns processadores desenvolvidos especialmente para o uso em FPGA. Tais processadores, em sua maioria, são comercializados pelos próprios fabricantes de dispositivos lógicos

-

<sup>&</sup>lt;sup>4</sup> Apesar da similaridade com a sigla designada para Computadores Pessoais (PC), optou-se pela denominação para contador de programa, visto que é o termo comumente encontrado na literatura técnica

<sup>&</sup>lt;sup>5</sup> Do inglês *Operation Code*, código de operação.

programáveis, sob a forma de núcleos de propriedade intelectual (IPs), desenvolvidos à partir de HDLs. Dentre os mais conhecidos *cores* voltados ao uso em FPGA, pode-se citar o PowerPC<sup>™</sup>, MicroBlaze<sup>™</sup> e PicoBlaze<sup>™</sup>, desenvolvidos pela empresa Xilinx (XILINX, 2007), além das plataformas NIOS e Excalibur desenvolvidas pela norte-americana Altera (ALTERA, 2012a).

## 2.4 NIOS II

Uma unidade central de processamento (CPU), comumente chamado de processador, é o principal componente dos computadores digitais. É a parte do computador responsável pela manipulação e transformação dos dados ou informações. Sua função é executar programas armazenados na memória principal, buscando suas instruções, examinando-as e executando-as uma após a outra (TANENBAUM, 1990).

Ao contrário dos processadores comumente utilizados, o processador NIOS II é um soft-core (núcleo de *hardware* implementado em arquivos-fonte HDL), pronto para ser utilizado em uma FPGA. Dessa forma ele pode ser configurado e expandido pela adição de novos componentes de *hardware*.

As principais características deste processador são vistas em Altera (2012b) e podem ser definidas como:

- Arquitetura RISC

- Pipeline opcional de 5 ou 6 estágios

- Arquitetura load-store

- Instruções de 32 bits

- Endereçamento de 32 bits

- 32 níveis de interrupção

- 32 registradores de propósito geral

- I/O mapeado em memória

- Unidade de gerenciamento de memória (MMU)

- Unidade de proteção de memória (MPU)

## Módulo de depuração JTAG

O processador NIOS II implementa uma arquitetura *Reduced Instruction Set Computer* (RISC), constituído por um pequeno e otimizado conjunto de instruções, em contraste com as máquinas CISC.

Segundo Heath (1991), em máquinas *Complex Instruction Set Computers* (CISC) 80% das instruções geradas e executadas usam somente 20% do set de instruções. Desta forma, ainda segundo Heath, se as instruções complexas forem sintetizadas em sequências de instruções simples, o *hardware* utilizado para implementá-las também pode ser reduzido em complexidade, sendo possível o desenvolvimento de processadores com maior desempenho, menor quantia de transistores e consequentemente menor custo.

Três doutrinas básicas podem definir a filosofia RISC (HEATH,1991):

- Todas as instruções devem ser executadas em um único ciclo de clock;

- A memória deve ser acessada somente via instruções de carga e armazenamento;

- Todas as unidades de execução devem estar fisicamente conectadas, sem nenhum microcódigo.

Outra das importantes características do processador NIOS II é seu *pipeline* de 5 ou 6 estágios. *Pipeline* pode ser definido como uma técnica de implementação de processadores que permite a sobreposição temporal das diversas fases de execução das instruções, aumentando assim o número de instruções executadas simultaneamente e a taxa de instruções iniciadas e terminadas por unidade de tempo. Quando carregada uma nova instrução, ela primeiramente passa pelo primeiro estágio, que trabalha nela durante apenas um ciclo, passando-a adiante, sendo processada sucessivamente pelos demais estágios do processador, enquanto os estágios anteriores já se ocupam com a execução da próxima instrução.

Uma das vantagens da técnica de *pipeline* é que o primeiro estágio não precisa ficar esperando a instrução passar por todos os demais para carregar a próxima, e pode carregar uma nova instrução assim que termina a primeira etapa. O *pipeline* não reduz o tempo gasto para completar cada instrução individualmente,

mas melhora o rendimento, pois várias tarefas são executadas simultaneamente usando recursos computacionais diferentes. Estas instruções são colocadas em uma fila de memória (dentro da CPU) e são executadas sequencialmente.

Os tempos de execução em processadores que utilizam técnicas de *pipeline podem* variar. Operações de ponto flutuante são muito sensíveis aos valores de dados, mas um *pipeline* de execução de inteiros (IEP) também pode introduzir variações dependentes dos dados. Em geral, o tempo de execução de uma instrução no *pipeline* não depende somente da instrução, mas também das instruções ao redor do *pipeline* (WOLF, 2001).

Existem atualmente três versões disponíveis do processador NIOS II, que apesar da diferenciação quanto a consumo de recursos e desempenho, compartilham o mesmo conjunto de instruções e nenhuma alteração no *software* é necessária para utilização em qualquer das três versões:

- Nios II/f Desenvolvido priorizando o desempenho de execução em detrimento ao uso de *hardware*. Possui um pipeline de 6 estágios, cache de instruções, cache de memória e predição de salto dinâmica.

- Nios II/s É o core padrão, desenvolvido visando um menor uso de portas lógicas, mantendo uma performance razoável. Possui pipeline de 5 estágios, cache de instruções e predição de salto estática.

- Nios II/e Otimizado para pequeno uso de recursos de hardware. N\u00e3o cont\u00e9m pipeline e cache.

O processador NIOS II utiliza portas separadas para instrução e dados. A porta de instruções somente executa operações de leitura para o carregamento das instruções. Já a porta de dados executa ambos, leitura e escrita, em memória ou periféricos, dependendo da instrução a ser realizada.

#### 2.4.1 Barramento Avalon

As duas portas, de instruções e de dados podem utilizar módulos de memória separados ou compartilhar os mesmos módulos de memória.

Em um sistema tradicional, o processador, a memória principal, os aceleradores e os dispositivos de I/O são conectados em um barramento compartilhado comum a todos. Como o barramento é um recurso compartilhado, o mesmo se torna um gargalo para a transferência de dados.

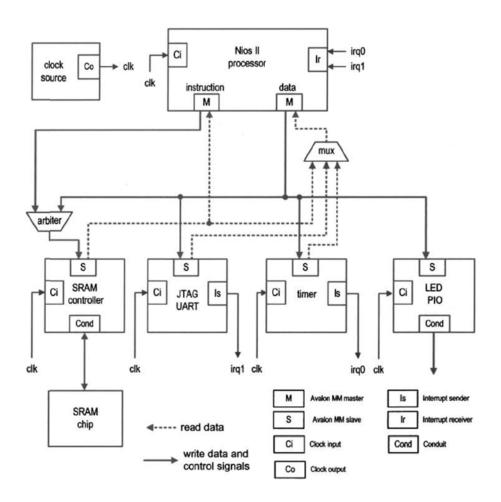

O processador Nios II, por sua vez, utiliza uma abordagem diferente. A plataforma *System on a Programmable Chip Builder* (SOPC Builder) da Altera provê a interconexão através de uma coleção de decodificadores, multiplexadores e árbitros, definindo caminhos concorrentes de transferência de dados, conforme mostrado na Figura 8.

Figura 8 - Implementação conceitual do barramento Avalon

Fonte: Chu (2011)

A interconexão é automaticamente gerada pelo software SOPC Builder no momento da compilação do hardware e se beneficia das características de

programabilidade da FPGA, gerando um *hardware* descentralizado e escalável, beneficiando assim o desempenho do sistema.

Para o desenvolvimento de um periférico de I/O ou um *hardware* acelerador, pode-se criar um circuito invólucro ao *hardware* funcional, para que o mesmo possa seguir a especificação do barramento Avalon, e dessa forma utilizá-lo como um componente integrado ao SOPC Builder.

O padrão Avalon consiste nos seguintes tipos de interface:

- Interface mapeada em memória (Avalon MM): Esta interface define uma conexão mestre-escravo baseada em endereço, onde um componente mestre utiliza um endereço para ler e escrever em um componente escravo.

- Interface de streaming Avalon (Avalon-ST): Define um link de comunicação unidirecional entre dois componentes, onde um componente Avalon-ST fonte transmite dados continuamente para outro Avalon-ST consumir.

- Interface escrava mapeada em memória tristate: É um caso especial de Avalon MM, utilizada para conexões a componentes tristate externos à FGPA, como memórias SRAM e Flash.

- Avalon clock: Define uma interface para sinais de clock e reset usados por um componente.

- Avalon interrupt: Define uma interface para que componentes escravos possam enviar eventos de interrupção para um componente mestre.

- Avalon conduit: Interface criada para agrupar e exportar dados para fora de um sistema SOPC Builder.

Como um periférico acelerador necessita comunicação baseada em endereços de memória, sempre sendo iniciada pelo dispositivo mestre, neste caso o processador NIOS II, a interface Avalon MM se mostra adequada a esta função.

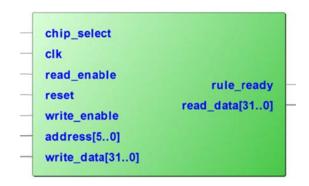

### 2.4.2 Interface Avalon MM

Esta interface basicamente define uma coleção de sinais e propriedades para padronizar a comunicação entre os componentes. Geralmente o processador NIOS II atua como único componente mestre e a maioria dos periféricos e aceleradores são componentes escravos. Como mestre ele pode iniciar a comunicação e solicitar a leitura ou escrita de dados em componentes escravos que, por sua vez, respondem a solicitação do mestre.

A interface de comunicação é composta por 22 sinais, dentre os quais os mais relevantes para o entendimento do periférico são:

- read (read\_n): sinal composto por um bit e usado para leitura de dados pelo mestre em um componente escravo.

- write (write\_n): sinal composto por um bit e usado para escrita de dados pelo mestre em um componente escravo.

- address: sinal com largura variável (1 a 32 bits) utilizado como offset de memória em um componente escravo. Cada valor identifica uma posição de memória interna ao compoenente.

- readdata: sinal com largura variável (8 a 1024 bits) onde os dados são entregues pelo componente escravo em uma operação de leitura.

- writedata: sinal com largura variável (8 a 1024 bits) onde os dados são entregues pelo componente mestre em uma operação de escrita.

- chipselect: sinal composto por um bit e utilizado pelo dispositivo mestre para selecionar um componente escravo para uma operação.

### 2.5 COPROCESSADORES

Um coprocessador pode ser definido como qualquer *hardware* que pode auxiliar um processador a desenvolver uma tarefa, ou um conjunto de tarefas de forma otimizada, trazendo dessa forma um benefício em desempenho ou economia de recursos. Ao assumir tarefas que consomem tempo de processamento, os coprocessadores podem acelerar a performance geral de um sistema (PATTERSON;HANNESSY, 2011).

Geralmente um coprocessador é um elemento passivo no sistema, recebendo dados de uma fonte, geralmente o próprio processador ou de acesso direto à sua memória e respondendo ao processador através de uma interrupção.

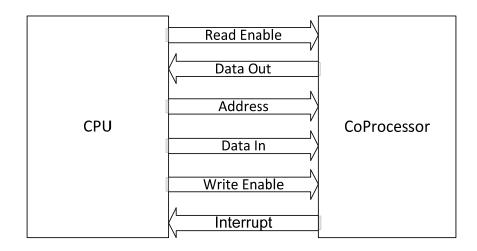

A Figura 9 apresenta a estrutura simplificada de um coprocessador mapeado em memória. Nesta figura pode-se observar os sinais utilizados para a comunicação com o mesmo. De forma genérica, o processador coloca um dado e um endereço no barramento e indica ao coprocessador com um sinal de write\_enable.

O coprocessador executa o tratamento dos dados recebidos e quando possui algum dado pronto indica ao processador com um sinal de interrupção. Quando o processador estiver disponível, informa ao barramento o endereço de leitura do coprocessador e indica a leitura através de um sinal e *read\_enable*.

Figura 9 – Modelo simplificado de um coprocessador

Fonte: própria

# 2.6 PARADIGMAS DE PROGRAMAÇÃO

Em Ciência da Computação, o termo paradigma é empregado como a maneira de compreender um problema do mundo real, para transformar este problema em uma solução computacional (BANASZEWSKI, 2009). Assim, um paradigma de programação determina a visão que o programador possui sobre a estruturação e execução do programa.

Neste âmbito, as linguagens de programação evoluem através do tempo. Linguagens já existentes evoluem agregando novas características e novas linguagens surgem apresentando características completamente diferentes das habituais de acordo com os conceitos de um novo paradigma de programação (BERGIN e GIBSON, 1996) (BANASZEWSKI, 2009).

Em meados de 1940, no início do advento dos computadores eletrônicos, a forma de programação era bastante precária, tornando-se uma atividade tediosa e bastante árdua. Os programadores precisavam compreender os detalhes da arquitetura do computador e adaptar a forma de pensar nos problemas computacionais de acordo com o processo de execução das instruções pelos computadores (BANASZEWSKI, 2009).

De forma geral, nessa época os programas eram escritos diretamente em linguagem de máquina, deixando todo o compreendimento de *hardware* e fluxo de execução do *software* por conta do programador.

Desde então as linguagens evoluíram muito, passando pelo surgimento da linguagem Assembly, em meados da década de 50, apresentando-se como forma de suprir a insatisfação dos programadores com a linguagem de máquina, chegando às linguagens de alto-nível, que oferecem comandos de manipulação mais próximos à linguagem humana, de forma que não seja necessário um conhecimento aprofundado da arquitetura dos computadores para criação de software (BANASZEWSKI, 2009).

A partir dessa ideia de linguagem de alto-nível, diversas linguagens surgiram, como COBOL, ALGOL e algum tempo depois - durante a década de 1960

- as linguagens estruturadas (C, PASCAL, BASIC). Esta linguagens tentavam suprir o problema de legibilidade e complexidade de código criado pelo comando "goto", usada nas linguagens não estruturadas para criar laços de repetição e desviar o fluxo do programa, o que os tornava de difícil entendimento e consequentemente manutenção complexa.

Em 1960, surge a linguagem LISP (abreviação de LISt Processing – Processamento de Listas), proposta como uma solução inovadora na programação, a qual permitiu melhoras significativas na abstração em relação às linguagens convencionais (e.g. recursividades, laços condicionais, *garbage collector*) (BANASZEWSKI, 2009).

Durante a década de 1970, surgem evoluções nas linguagens imperativas e declarativas, juntamente com os sistemas baseados em regras, permitindo a representação do mundo real por meio de objetos computacionais, de forma semelhante à maneira como um humano percebe o mundo, oferecendo uma maior proximidade da forma de estruturar os problemas computacionais à cognição humana (NEWEL; SIMON, 1972) (BANASZEWSKI, 2009).

Com esse pressuposto, diversas linguagens imperativas surgiram, como SIMULA, Smalltalk, Object Pascal, C++ e Java, que ainda são largamente utilizadas nos dias de hoje. Em paralelo à melhoria das linguagens imperativas, surge uma nova linguagem declarativa, a linguagem PROLOG (PROgrammation in LOGic) permitindo desenvolver soluções computacionais da mesma maneira que se organiza o conhecimento para raciocinar. Esta linguagem é baseada em texto escrito em linguagem supostamente "natural", onde as relações lógicas são representadas por meio de Regras. Na Figura 10, pode-se observar a evolução de destas linguagens, relacionadas com seus respectivos paradigmas.

Figura 10 - Evolução das linguagens em relação aos paradigmas de programação

Fonte: Banaszewsk (2009)

A programação declarativa demandaria menos esforços de programação do que a programação imperativa. Por outro lado, perde-se flexibilidade na programação, principalmente para otimizar o código em termos de acesso ao hardware e desempenho. Isto porque as linguagens declarativas demandam buscas propriamente ditas, para correlacionar as expressões causais e os estados de entidades computacionais (e.g. variáveis ou atributos de objetos), avaliando por meio de algoritmos e estruturas de dados, que são caras computacionalmente (BANASZEWSKI, 2009).

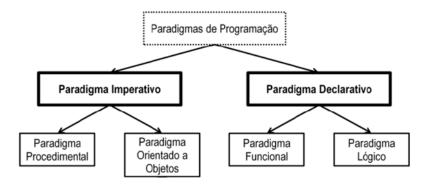

Isto dito, o conjunto de paradigmas de programação estabelecidos é chamado de paradigmas dominantes. Entre os Paradigmas dominantes estão o Paradigma Procedimental (PP), o Paradigma Funcional (PF), o Paradigma Orientado a Objetos (POO) e o Paradigma Lógico (PL) (BANASZEWSKI, 2009). Na Figura 11 pode-se ver uma dada interpretação de relação entre os paradigmas existentes atualmente.

Figura 11 - Classificação dos atuais paradigmas

Fonte: (adaptado de BANASZEWSKI, 2009)

O Paradigma Imperativo consiste na organização sequencial do *software* por meio de comandos em uma linguagem procedimental ou orientada a objetos, os quais são executados sequencialmente pelo mecanismo interno destas linguagens. Basicamente, este mecanismo consiste em "buscas" sobre variáveis, vetores e listas e aos comandos de decisão e fluxo de execução.

Devido à sequencialidade da busca e a passividade dos buscados nas linguagens do PI, as linhas de código se tornam interdependentes e há problemas de redundância na execução dos programas (BANASZEWSKI, 2009). Estas redundâncias em sistemas compostos por muitas expressões de decisão possuem efeitos no desempenho da aplicação, podendo chegar a níveis inaceitáveis (SIMÃO; STADZISZ, 2008).

Comumente, nos programas criados com os conceitos do Paradigma Imperativo, o código referente à solução propriamente dita encontra-se disperso entre os comandos e expressões da própria linguagem, tornando o entendimento do código uma tarefa árdua, além de desviar a atenção do programador para à linguagem e não para o problema a ser resolvido.

O Paradigma Declarativo, por sua vez, é caracterizado pela interação mais simplificada do programador com o computador por meio de mecanismos que escondem as particularidades de implementação. No Paradigma Declarativo, o programador se concentra mais na organização do conhecimento sobre a resolução

do problema computacional do que na implementação do mesmo (BANASZEWSKI, 2009).

Porém, para oferecer estas facilidades o Paradigma Declarativo perde em velocidade de execução para o Paradigma Imperativo e em certas flexibilidades, especialmente no acesso direto ao *hardware* (SCOTT, 2000). Dessa forma, uso destas soluções pode limitar a criatividade do programador e também o acesso aos componentes de *hardware* ou ainda impossibilitar a construção de códigos mais eficientes, uma vez que os comandos declarativos são implementados para uso genérico (BANASZEWSKI, 2009).

Outrossim, todos estes paradigmas levam ao forte acoplamento de expressões causais e redundâncias decorrentes das suas avaliações. Estas limitações dificultam a execução paralela ou distribuída de programas e frequentemente comprometem o seu desempenho pleno mesmo em sistemas monoprocessados. Assim, existem motivações para buscas de alternativas à tais paradigmas com objetivo de suprir as desvantagens apresentadas (BANASZEWSKI, 2009).

Com este foco, foi concebido o Paradigma Orientado a Notificações (PON), introduzido embrionariamente em (SIMÃO, 2001) e (SIMÃO, 2005) e detalhado em (SIMÃO;STADZISZ, 2008) (SIMÃO;STADZISZ, 2008) (BANASZEWSKI, 2009), propondo soluções efetivas para as deficiências apresentadas e se apresentando como um paradigma com grande potencial de aplicabilidade (SIMÃO et al, 2012d).

# 2.7 PARADIGMA ORIENTADO A NOTIFICAÇÕES

O Paradigma Orientado a Notificações (PON) é uma alternativa aos atuais paradigmas de programação (eg. imperativo, declarativo e orientado a objetos), se inspirando-se e evoluindo a partir dos mesmos, com ênfase nos conceitos dos Sistemas Baseados em Regras (SBR), os quais oferecem (até então) modelos de programação com maior proximidade à cognição humana (NEWEL; SIMON, 1972).

PON visa eliminar algumas das principais deficiências dos atuais paradigmas, como a existência de avaliações causais desnecessárias e fortemente acopladas.

Atualmente, os conceitos do PON estão materializados como um *framework* para uma linguagem de programação imperativa, a linguagem C++, por meio da qual os elementos do PON (eg. Atributos, Premissas, Condições, Regras etc) são representados como objetos C++. Entretanto, por ser inspirado em conceitos do paradigma declarativo, o *framework* do PON trás maiores facilidades de programação à linguagem C++, as quais são similares àquelas ofertadas na programação declarativa.

A programação em PON, por seguir os conceitos dos Sistemas Baseados em Regras, se torna mais fácil, se aproximando à forma cognitiva humana, permitindo a representação do conhecimento de forma natural ao ser humano, o PON também visa alcançar esforços mínimos na programação em termos de escrita de código (BANASZEWSKI, 2009).

Essencialmente, a programação em PON consiste em conceber os relacionamentos entre elementos da base de fatos (FBEs) por meio de Regras (Rules), onde o programador somente precisa compor as Regras sem necessariamente se preocupar em como elas vão interagir para que o fluxo de execução seja estabelecido, principalmente se uma ferramenta *wizard* for utilizada (BANASZEWSKI, 2009).

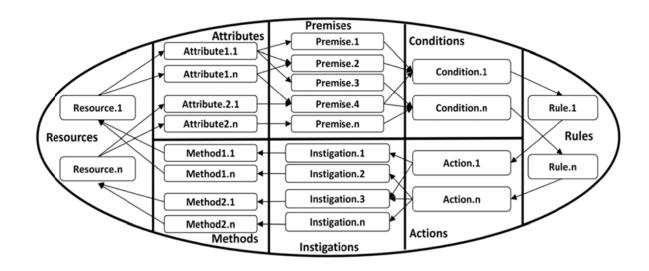

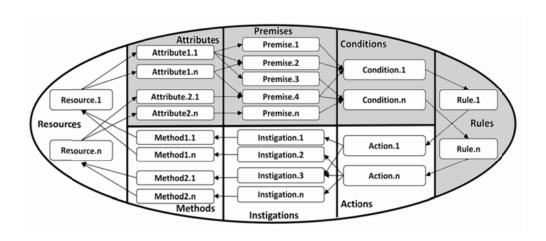

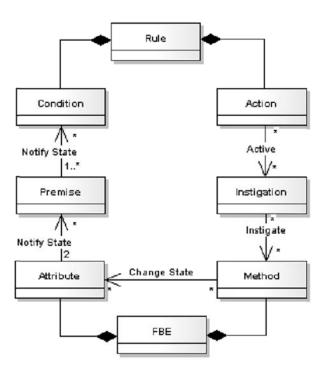

Uma aplicação em PON é formada a partir da combinação de diversos objetos desacoplados que interagem entre si para implementar as funcionalidades desejadas. Os principais componentes do PON são: elementos da base de fatos (*Fact Base Elements*, ou FBEs), Atributos (*Attributes*), Premissas (*Premises*), condições (*Conditions*), Regras (*Rules*), ações (*Actions*), instigações (*Instigations*) e métodos (*Methods*) (BANASZEWSKI, 2009).

Na Figura 12 pode-se observar a cadeia de notificações criada, onde um objeto do tipo Atributo se comunica com objetos do tipo Premissa, dando início à cadeia de notificações. As Premissas se comunicam com as Condições, notificando-as quando necessário. As condições, por sua vez, quando verdadeiras ativam as Regras, que dão início às Ações, Instigações e Métodos, conforme necessário.

Todos os objetos somente são executados, quando um objeto correlacionado o notifica, minimizando o ciclo de execução e evitando processamento desnecessário.

Figura 12. Exemplo da cadeia de notificações formada pelos componentes do PON

Fonte: Banaszewski (2009).

### 2.7.1 Elementos da Base de Fatos

Em PON, um Elemento da Base de Fatos descreve estados e serviços de entidades (reais ou computacionais) de um dado problema. Essencialmente, cada FBE representa os estados, serviços e entidades por meio de Atributos e Métodos (SIMÃO et al, 2012d).

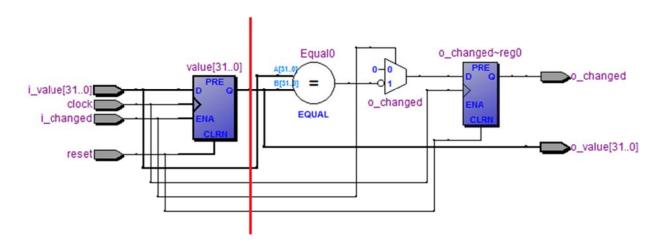

#### 2.7.2 Atributos

Os Atributos do PON diferem das demais linguagens por ter uma conotação ativa. Além de armazenar um valor, como nas demais linguagens, ele também é responsável por notificar as estruturas pertinentes (Premissas) sobre alterações em seu valor, dando inicio a cadeia de notificações do PON. Ainda pode-se dizer, em termos gerais, que o conjunto de Atributos de um sistema compõe o seu estado atual.

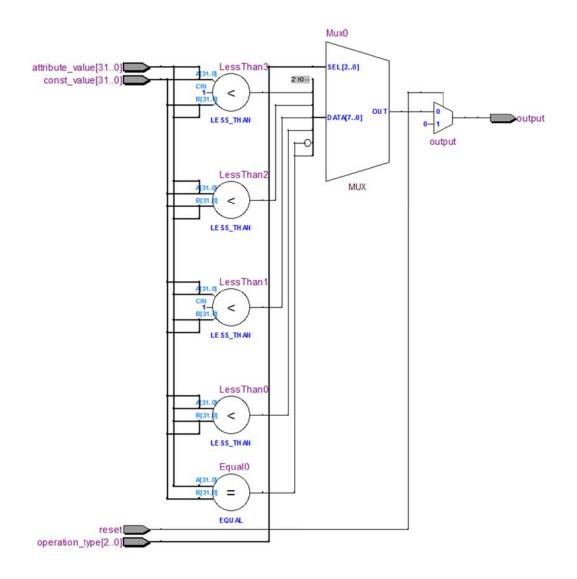

#### 2.7.3 Premissas

Uma Premissa em PON consiste em uma operação lógica sobre o valor de um Atributo e um valor constante ou valor de outra premissa. Esta operação lógica é realizada no momento em que um Atributo notifica à Premissa sobre a alteração em seu valor armazenado. Quanto a operação lógica realizada, uma Premissa pode ser configurada para as operações lógicas igual a, diferente de, maior que, maior ou igual a, menor que e menor ou igual a (SIMÃO et al, 2012d).

No momento de sua alteração, as Premissas precisam notificar suas estruturas subsequentes, neste caso as condições, repassando seu estado lógico e dando continuidade à cadeia de notificação do PON (SIMÃO et al, 2012d).

### 2.7.4 Condições

Uma Condição representa uma expressão lógico-causal sobre os valores de saída das Premissas. Cada entidade Condição notificada reavalia o seu estado lógico de acordo com o valor recém-notificado pela Premissa em questão juntamente como os valores notificados previamente pelas demais Premissas conectadas. Assim, quando todas as Premissas que compõem uma Condição apresentam o estado lógico verdadeiro, a entidade Condição é satisfeita e sua Regra relacionada é aprovada. A operação realizada pode ser uma conjunção ou uma disjunção lógica sobre as saídas das Premissas, representando um conjunto de Premissas ativas ou não ativas (SIMÃO et al, 2012d).

Assim como os Atributos e as Premissas, as condições também precisam repassar às estruturas subsequentes, neste caso as Regras, o valor de saída da operação realizada, além de uma notificação quando este valor for alterado (SIMÃO et al, 2012d).

### 2.7.5 Regras

Um objeto Regra é a composição de dois objetos, uma Condição e uma Ação, tendo por finalidade descrever um aspecto específico da lógica de negócios da aplicação implementada. Em termos de componentes do PON, uma Regra simplesmente conecta uma Condição a uma ação, que será executada quando a Condição for verdadeira (SIMÃO et al, 2012d).

Ao invés de serem executadas imediatamente após suas condições se tornarem verdadeiras, as Regras são apenas aprovadas para execução, e sua execução é controlada por um objeto *Scheduler*, o qual pode considerar outros fatores, como prioridades relativas entre as Regras ou estratégias de resolução de conflitos (SIMÃO et al, 2012d) (BANASZEWSKI, 2009).

### 2.7.6 Ações

Uma ação corresponde a um conjunto de tarefas que serão executadas quando uma Regra for aprovada para execução e um parâmetro configurável, indicando se estas tarefas deverão ser executadas simultaneamente ou sequencialmente. Estas tarefas estão encapsuladas em outro componente do PON, a instigação (SIMÃO et al, 2012d).

### 2.7.7 Instigações

Uma instigação no PON possui duas responsabilidades, podendo tanto redefinir o estado de um Atributo, reiniciando a cadeia de notificações, quanto iniciar a execução de um método (SIMÃO et al, 2012d).

#### 2.7.8 Métodos

Um método na atual implementação do PON equivale a um método (função) da linguagem C++. Esta funcionalidade possibilita a integração de uma aplicação em PON com código imperativo tradicional.

Desta forma, o programador possui liberdade para realizar praticamente qualquer tipo de operação dentro de um método, independentemente de sua complexidade ou duração. Na implementação atual em C++, um método não possui valor de retorno; porém, isto é contornado devido à facilidade de interagir com os componentes do PON dentro do próprio método (por exemplo, redefinindo o valor de um Atributo ao término de sua execução).

### 2.8 REFLEXÃO

Em suma, os conceitos do PON surgem para tornar a programação mais simples. Além de permitir a estruturação do conhecimento em forma natural ao ser humano. Proporciona a composição deste conhecimento de forma simplificada e transparente das particularidades do código imperativo. No mais, quando estas particularidades se fazem necessárias, o PON possibilita o seu uso, porém o faz de forma a evitar a ocorrência de certos problemas natos a este tipo de programação, como o acoplamento, dispersão do conhecimento e execuções desnecessárias (BANASZEWSKI, 2009).

Por ser composta de uma cadeia de pequenas entidades computacionais desacopladas, comunicando-se assincronamente, somente quando há necessidade, o PON torna-se é um bom candidato a implementação direta em *hardware*. No capítulo seguinte, tal implementação é descrita.

#### 3 DESENVOLVIMENTO

# 3.1 INTRODUÇÃO

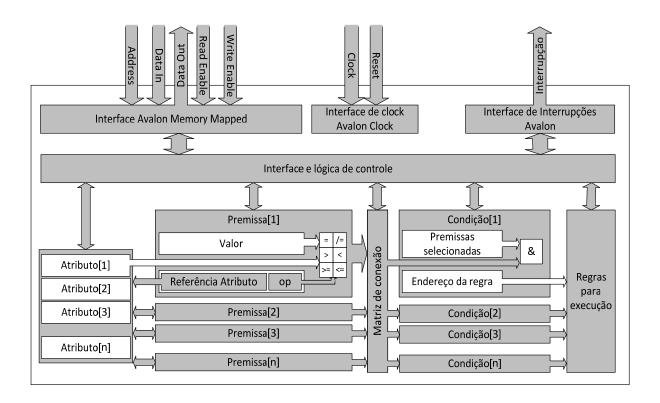

Para eliminar os gargalos associados à implementação puramente em software do PON, implementou-se um hardware coprocessador (CoPON) capaz de executar toda a cadeia de inferências (Atributos, Premissas, condições e partes das Regras).

A estrutura fundamental do periférico PON se baseia em converter os componentes não dinâmicos do paradigma em componentes de *hardware*. Com isso, têm-se a intenção de substituir todo o processamento da cadeia de notificações e das operações lógicas por um *hardware* equivalente, liberando o processador dessa tarefa. A cadeia de notificações e as expressões lógicas possuem um alto custo computacional quando executadas puramente em *software*, já que necessitam estruturas complexas para que possam ser executadas sobre uma linguagem de programação genérica. Dessa forma substituí-las por um *hardware* capaz de desempenhar a mesma função poderá ocasionar um grande ganho na eficiência geral do sistema.

Este capítulo apresenta uma série de metodologias e ferramentas utilizadas no desenvolvimento do Coprocessador para Paradigma Orientado a Notificações (CoPON), bem como o funcionamento do *hardware* propriamente dito.

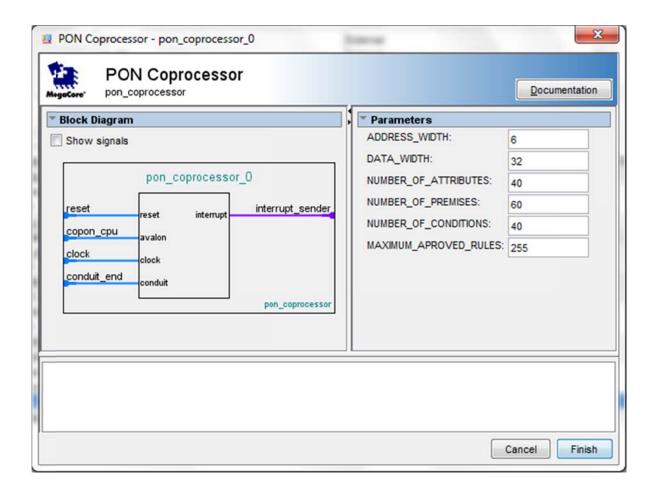

Optou-se pela criação de um *hardware* totalmente configurável quanto ao número de componentes PON de cada tipo presentes no sistema final. No momento da criação do sistema no aplicativo Altera SOPC Builder, configura-se o número de Atributos, Premissas, condições e Regras que o sistema suportará. Os valores máximos somente são limitados pela disponibilidade física de unidades lógicas e memória na FPGA.

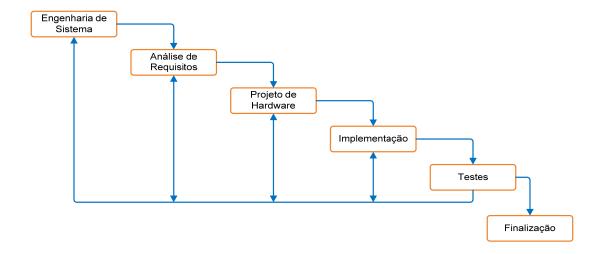

O desenvolvimento da arquitetura do sistema envolveu diversas etapas complementares entre si, numa sequência de atividades similares às aplicadas em

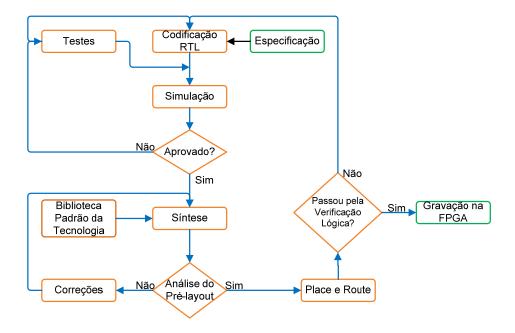

projetos de engenharia. Utilizou-se para este caso o Modelo Clássico de Desenvolvimento ou Modelo em Cascata, o qual é demonstrado através da Figura 13 abaixo.

Figura 13 - Modelo Clássico de Desenvolvimento

Fonte: Própria

Este modelo propõe uma abordagem sistemática e sequencial ao desenvolvimento do sistema, que começa pela definição de requisitos do sistema e passa pela análise, projeto, codificação e teste. Durante qualquer das etapas, pode ser necessário retornar para etapas anteriores e reiniciar o ciclo.

#### 3.2 DESENVOLVIMENTO DO HARDWARE EM HDL

O modelo de desenvolvimento utilizado para sistemas baseados em linguagens de descrição de *hardware* pode ser sumarizado através da Figura 14. Nele pode-se observar as diversas etapas envolvidas na criação do sistema, desde a sua especificação até a finalização do projeto.

Figura 14 - Fluxo de desenvolvimento de sistemas baseados em HDLs

Fonte: adaptado de Lee (2003)

As etapas mais importantes do desenvolvimento dos sistemas em lógica programável e apresentadas na figura anterior são descritos abaixo.

### 3.2.1 Especificação e Desenho

Neste estágio, são definidos os parâmetros mais importantes do sistema que se está planejando. Nele são definidas de forma genérica todas as funções que o sistema suportará, suas interfaces externas e suas respostas externas.

A partir dos parâmetros definidos, são definidos vários blocos com a lógica do sistema e como estes se comunicarão.

### 3.2.2 Micro Desenho

Nesta fase é descreve-se o funcionamento de cada um dos blocos. O micro desenho contém detalhes sobre máquinas de estado, contadores, registradores

internos e possíveis formas de onda de saída. Esta é uma das fases que demanda mais tempo no desenvolvimento.

### 3.2.3 Codificação em Nível de Transferência de Registro – RTL

Nesta etapa, o micro desenho é convertido em arquivos HDL com a síntese da linguagem utilizada, seja ela Verilog, VHDL ou outra qualquer. Todo o trabalho de geração dos arquivos-fonte é executado nesta etapa, convertendo todo o *hardware* planejado em arquivos de texto com a descrição do sistema.

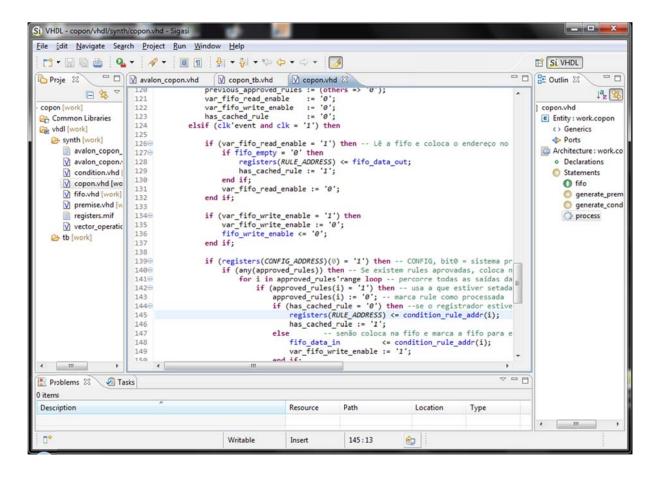

Para o desenvolvimento desse sistema, utilizou-se a linguagem VHDL e o ambiente integrado de desenvolvimento (IDE) para *Hardware*, Sigasi 2.0, mostrado na Figura 15.

Figura 15 - Ambiente integrado de desenvolvimento para VHDL

Fonte: Própria

Esta IDE provê diversos recursos úteis para a codificação, como análise de erros de código em tempo real e ferramentas para refatoração de código.

### 3.2.4 Simulação e Testes

Simulação é o processo de verificação das características funcionais e temporais dos modelos criados. Para tanto usualmente cria-se arquivos de testes (testbenches), com os sinais de clock, reset e demais dados das entradas do bloco a ser testado, de forma que se possa analisar o funcionamento do bloco através das saídas do mesmo. Segundo Lee (2003), de 60% a 70% do tempo despendido com o desenvolvimento ocorre na verificação do sistema.

Cada componente do PON utilizado para a criação do periférico foi simulado e testado individualmente. Além dos testes individuais, também fez-se necessário a criação de um teste de integração do sistema, onde todos os sinais de entrada do periférico, que na prática serão gerados pelo NIOS II, foram simulados, garantindo a comunicação e integração de todos os componentes como um sistema.

Para a realização dos testes, utilizou-se o simulador de VHDL ModelSim Altera Starter Edition, versão 10.0c, e scripts auxiliares desenvolvidos em linguagem Ruby, para automatização de tais testes.

#### 3.2.5 Síntese, Alocação e Roteamento

Síntese é o processo em que o compilador transforma o sistema descrito através de arquivos HDL na tecnologia do dispositivo de lógica programável a ser utilizado. Neste processo, são geradas as listas de ligações com os componentes que serão utilizados.

Alocação e roteamento é a etapa posterior à síntese, onde todas as portas lógicas e *flip-flops*<sup>6</sup> são distribuídas. A distribuição dos sinais de relógio e *reset* são feitas e depois disso, cada bloco é roteado dentro da FPGA.

Cada fabricante de FPGAs possui seu sistema proprietário para síntese e, nesse caso, por se tratar de um periférico para o processador NIOS II da Altera, utilizou-se a ferramenta Quartus II 11.1 para esta tarefa.

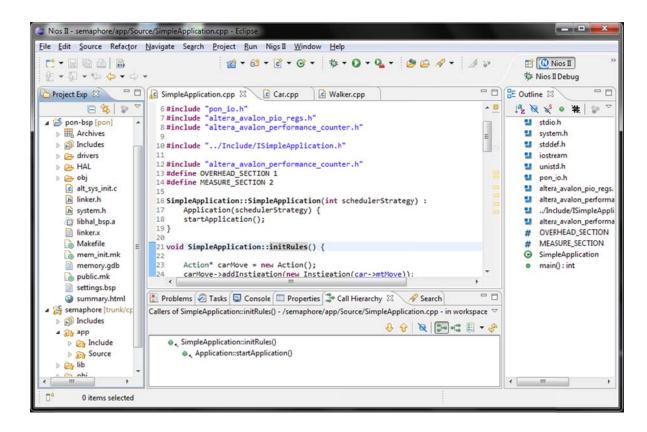

### 3.3 DESENVOLVIMENTO DE SOFTWARE

Para o desenvolvimento do *software* para o processador NIOS II, bem como todo o SoC gerado, utilizou-se as ferramentas fornecidas pela fabricante da FPGA. A suíte de ferramentas utilizada, *Nios II Software Build Tools (SBT)* é compostas por compilador, *linker* e *debugger*, disponíveis na IDE Eclipse, com o *plugin* Nios II *SBT for Eclipse*<sup>TM</sup>, conforme apresentado na Figura 16.

As ferramentas presentes nesta suíte, além de permitirem o desenvolvimento do código da aplicação propriamente dito, criam todas as interfaces de *hardware* necessárias ao desenvolvimento, através da ferramenta *Board Suport Package* (BSP). Esta ferramenta utiliza como entrada o arquivo ".sopcinfo", gerado no momento da criação do sistema, criando através dele arquivos de cabeçalho contendo o mapa de memória do sistema e funções de acesso ao *hardware*.

As linguagens disponíveis para criação de *software* para esta plataforma são Assembly e C/C++, sendo que a utilizada para este projeto foi a C++, mantendo assim a compatibilidade com o *framework* já desenvolvido para o PON.

-

<sup>&</sup>lt;sup>6</sup> Os flip-flops são elementos de circuito que podem apresentar em seu funcionamento apenas dois estados estáveis. Não existem estados intermediários entre estes dois estados.

Figura 16 - Ambiente integrado de desenvolvimento SBT

Fonte: Própria

Para validação do sistema, criaram-se dois conjuntos de *software*s, um orientado totalmente a teste funcional do sistema e outro que visa validar o sistema comparando-o com implementações anteriores do PON.

O software de teste funcional tem por finalidade estressar todas as funções existentes no hardware, utilizando a mesma lógica utilizadas nos testes de hardware. Com este software todo o hardware desenvolvido é previamente testado, garantindo assim seu funcionamento de acordo com o projeto especificado.

Para o segundo grupo de aplicações, alguns dos programas anteriormente escritos utilizando o *framework* PON foram portados e executados na plataforma NIOS II. Para comparação, criou-se um *software* equivalente funcionalmente utilizando o coprocessador, e uma variação do *framework*, que tem por finalidade configurar e utilizar o coprocessador mantendo a mesma interface de aplicação (API) do PON puramente em *software*.

As alterações feitas no atual *framework* para o PON visam configurar e utilizar o coprocessador de forma transparente ao usuário. Dessa forma grande parte das aplicações já desenvolvidas utilizando-se o PON podem ser reutilizadas, com alterações mínimas no código.

Aplicações que utilizam apenas Atributos, Premissas, Condições e Regras simples são completamente suportadas. Já casos onde se utilizam recursos avançados do PON, como Sub-Condições não são suportados pela atual versão do CoPON. Em alguns casos podemos contornar as limitações através de artifícios de software, que devem ser analisados para cada situação.

### 3.4 ESTRUTURA DO PON EM HARDWARE

O fato de o PON ser representado com uma cadeia de entidades computacionais simples e imutáveis, operando em paralelo, traz indícios de que o mesmo possa ser adequado à implementação em *hardware*.

Analisando-se o atual *framework*, criado para materializar as ideias referentes ao paradigma orientado a notificações, pode-se concluir que Atributos, Premissas, condições e partes das Regras podem trazer benefícios se implementados em *hardware*, sem trazer prejuízos à usabilidade do *framework*. Os demais componentes podem assumir diferentes formas, e dependem exclusivamente da aplicação em questão para sua criação (JASINSKI, 2012).

Um Método, por exemplo, é composto diretamente por código C++ e pode servir de interface entre o código escrito utilizando o PON e código imperativo tradicional. Dessa maneira, se o mesmo for implementado em *hardware*, pode-se perder em flexibilidade no *framework* já a interligação entre *software* PON e código legado será dificultada.

Optou-se por desenvolver os componentes indicados na Figura 17 (Atributos, Premissas, condições e Regras), criando um *hardware* genérico que poderá ser utilizado por qualquer aplicação que siga o PON. O *hardware* gerado visa eliminar os gargalos associados com a implementação do PON puramente em

software, transferindo a carga de processamento diretamente para um coprocessador (CoPON).

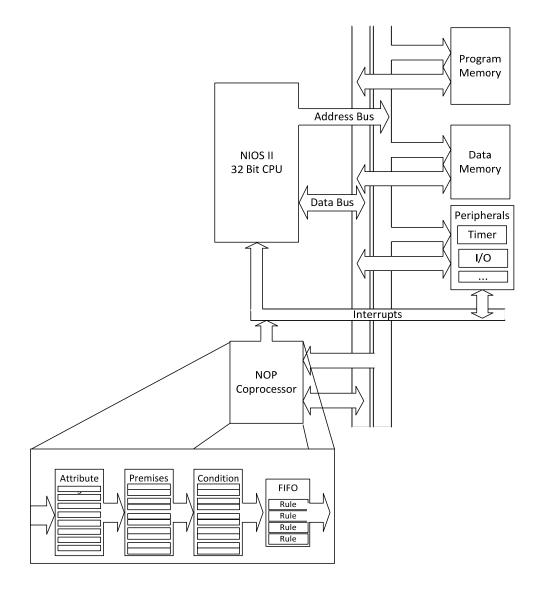

Este coprocessador foi implementado como um periférico para o processador NIOS II e é capaz de executar toda a cadeia de inferências, reduzindo o uso de recursos de processamento pelo *software*. O SoC resultante é constituído do processador, módulos de memória, periféricos de I/O e o periférico acelerador, compartilhando o mesmo endereçamento de memória, permitindo um uso transparente do coprocessador pelo *software*, como pode-se ver, por exemplo na Figura 18. Nesta figura observa-se a forma com que o coprocessador é conectado ao processador, através dos barramentos de dados e de endereços. Pode-se ver também o compartilhamento entre os periféricos do canal de interrupção do sistema.

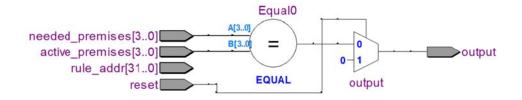

Figura 17 - Representação dos componentes implementados no periférico

Fonte: adaptado de Banaszewski (2009)

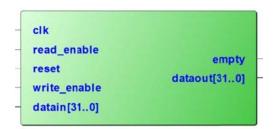

Figura 18 - Representação geral do sistema